# WWVB SYNCHRONIZED CLOCK

MODEL 8170

# INSTRUCTION MANUAL

www.spectracomcorp.com • sales@spectracomcorp.com 95 Methodist Hill Drive • Rochester, NY 14623 USA Phone: +1.585.321.5800 • Fax: +1.585.321.5218

Manual Revision 1.0 0740-00000 Revision, if any, are located at back. April 1988

|           | IADLE OF CONTENTS                                                                                                                               | PAGE                                                                        |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| SECTION 1 | Installation & Operation                                                                                                                        | 1-1                                                                         |

| 1.1       | Introduction                                                                                                                                    | . 1-2                                                                       |

| 1.2       | Installation                                                                                                                                    | . 1-2<br>1-2<br>1-2<br>1-3<br>1-3<br>1-6<br>1-6<br>1-6<br>1-8<br>1-8<br>1-9 |

| 1.3       | Operation                                                                                                                                       | 1-9 1-9 1-10 1-11 1-12 1-13 1-14 1-15 1-16 1-18 1-19 1-19                   |

| SECTION 2 | Theory of Operation                                                                                                                             | . 2-1                                                                       |

| 2.1       | Introduction                                                                                                                                    | 2-2                                                                         |

| 2.2       | Mainframe Schematic                                                                                                                             | 2-2                                                                         |

| 2.3       | Al, RF Amplifier, Part Number 001100                                                                                                            | 2-2                                                                         |

| 2.4       | A2, Receiver Assembly, Part Number 001200-1 2.4.1 Phase Locked Loop 2.4.2 AGC Loop 2.4.3 Phase Detector Balance Adjustment 2.4.4 Power Supplies | 2-6<br>2-6<br>2-7<br>2-8<br>2-8                                             |

| 2.5       | A3, Microprocessor Assembly Part Number 014800 .                                                                                                | 2-13                                                                        |

| 2.6       | A4, Display Assembly, Part Number 014100                                                                                                        | 2-21                                                                        |

| 2.7       | Power Transformer                                                                                                                               | 2-21                                                                        |

# TABLE OF CONTENTS

| SECTION 3 | Service Information                                 | .3-1         |  |  |

|-----------|-----------------------------------------------------|--------------|--|--|

| 3.1       | Calibration of the Model 8170                       | .3-2         |  |  |

| 3.2       | Alignment Procedures                                | .3-2         |  |  |

|           | 3.2.1 RF Amplifier Assembly (A1 Board, Fig. 3-2) 3- |              |  |  |

|           | 3.2.2 Receiver Assembly (A2 Board, Fig. 3-3)        | 3-5          |  |  |

| 3.3       | Antenna (Model 8206) Test Procedure                 |              |  |  |

| 3.4       | Model 8207 Preamplifier Alignment                   | .3-10        |  |  |

| 3.5       | Trouble Shooting                                    |              |  |  |

|           | 3.5.1 Receiver                                      | 3-11         |  |  |

|           | 3.5.2 Microprocessor                                | 3-13         |  |  |

| 3.6       | Microprocessor and Display Assembly                 | .3-13        |  |  |

| SECTION 4 | Model 8170 Options                                  | .4-1         |  |  |

|           | 4.1.0 Option 15 - Timing Pulse Outputs              | 4-2          |  |  |

|           | 4.1.1 Option 15 - Principles of Operation           | 4-2          |  |  |

|           | 4.2.0 Option 18 - Parallel BCD Output               | 4-5          |  |  |

|           | 4.2.1 Option 18 - Principles of Operation           | 4-6          |  |  |

|           | 4.2.2 Option 18 - Performance Checks                | 4-7          |  |  |

|           | 4.3.0 Option 19 - Remote Output Driver              | 4-8          |  |  |

|           | 4.3.1 Option 19 - Specifications                    | 4-8          |  |  |

|           | 4.3.2 Option 19 - Principles of Operation           | 4-10         |  |  |

|           | 4.3.3 Option 19 - Performance Checks                | 4-11         |  |  |

|           | 4.4.0 Option 23 - IRIG B Output                     | 4-13         |  |  |

|           | 4.4.1 Option 23 - Specifications                    | 4-13         |  |  |

|           | 4.4.2 Option 23 - Internal Switches                 | 4-16         |  |  |

|           | 4.4.3 Option 23 - Principles of Operation           | 4-16         |  |  |

|           | 4.4.4 Option 23 - Performance Checks                | 4–17         |  |  |

|           | 4.5.0 Option 24 and 25 - TCXO and External          |              |  |  |

|           | Oscillator Input                                    | 4-20         |  |  |

|           | 4.5.1 Option 24 and 25 - Specifications             | 4-20         |  |  |

|           | 4.5.2 Option 24 and 25 - Principles of Operation    |              |  |  |

|           | 4.5.3 Option 24 and 25 - Performance Checks         | 4-24<br>4-24 |  |  |

|           | 4.5.3.1 Test Equipment 4.5.3.2 Test Purpose         | 4-24         |  |  |

|           | 4.5.3.3 Test Set-Up                                 | 4-25         |  |  |

|           | 4.5.3.4 Test Procedure                              | 4-25         |  |  |

|           | 4.6.0 Option 28 - 1 KHz Output                      | 4-27         |  |  |

|           | 4.6.1 Option 28 - Principles of Operation           | 4-27         |  |  |

|           |                                                     |              |  |  |

|           | 4.7.0 Option 30 - Fully Decoded Text Stream         | 4-30         |  |  |

|           | 4.7.1 Option 30 - Principles of Operation           | 4-30         |  |  |

|           | 4.7.2 Option 30 - Performance Checks                | 4-30         |  |  |

|           |                                                     |              |  |  |

|           |                                                     |              |  |  |

# LIST OF ILLUSTRATIONS

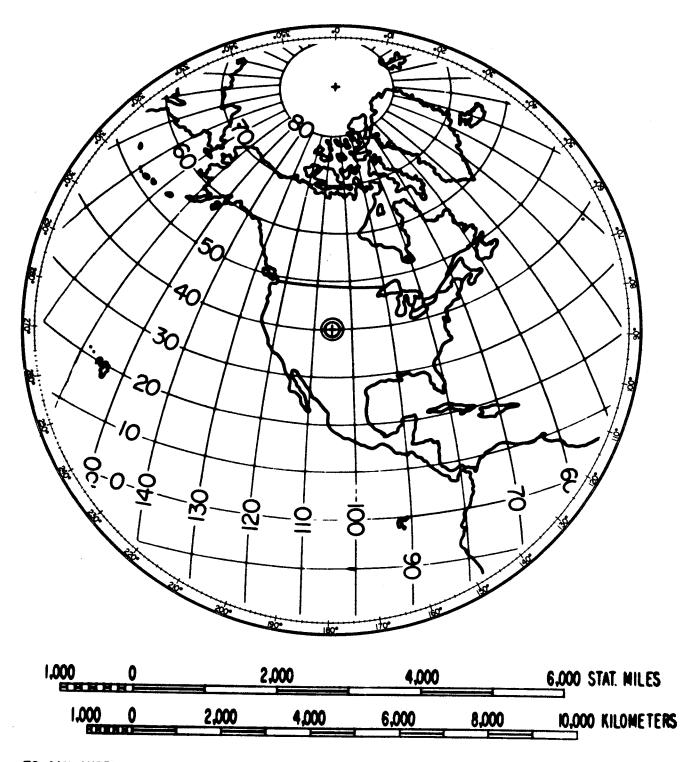

| FIG. | 1-1  | Great Circle Map                            | 1-4  |

|------|------|---------------------------------------------|------|

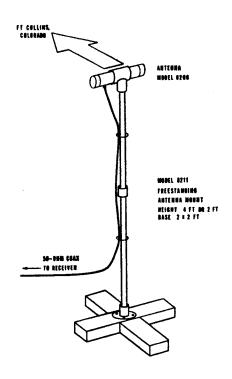

|      | 1-2  | Antenna Mount Model 8211                    | 1-5  |

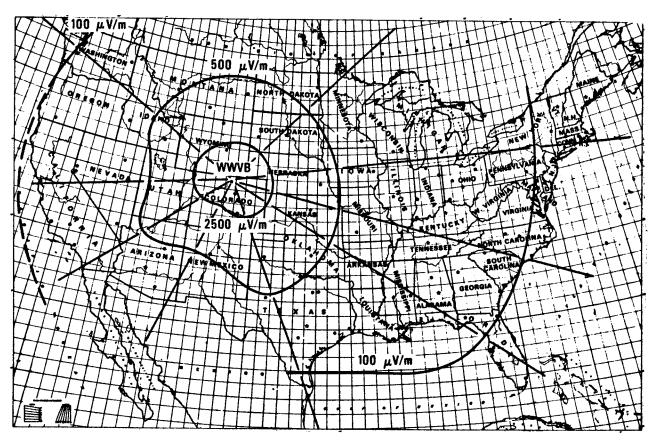

|      | 1-3  | Signal Strength Map                         | 1-5  |

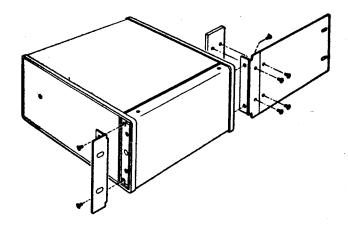

|      | 1-4  | Rack Mount Option 01                        | 1-7  |

|      | 1-5  | Rack Mount with Slides - (Option 11)        | 1-7  |

|      | 1-6  | Sample Memory Dump                          | 1-17 |

|      | 1-7  | WWVB Time Code Format                       | 1-17 |

|      | 1-8  | Path Delay Map                              | 1-20 |

| FIG. | 2-1  | Mainframe Schematic                         | 2-3  |

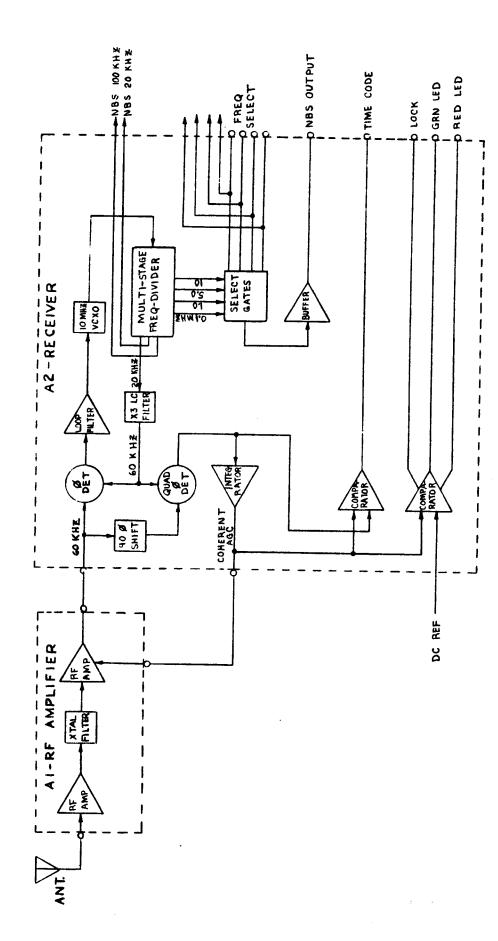

|      | 2-2  | Receiver Block Diagram                      | 2-4  |

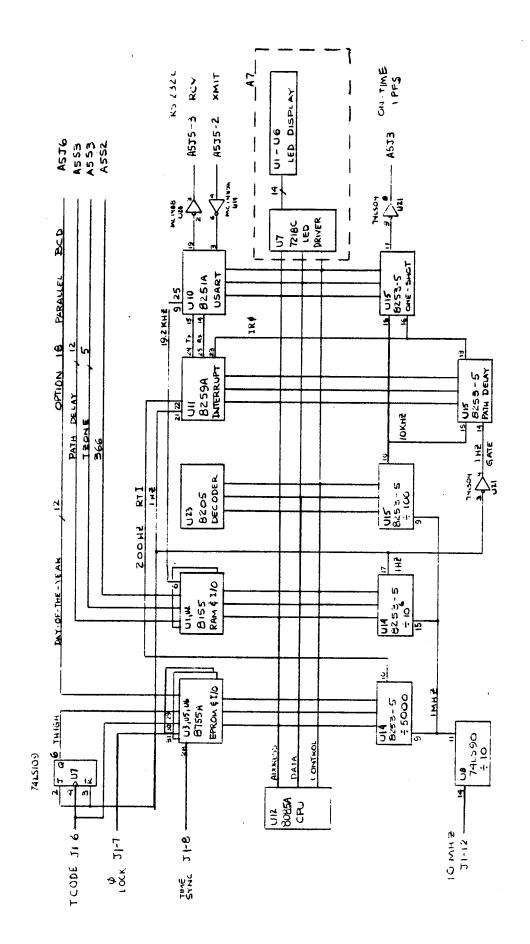

|      | 2-3  | Microprocessor Block Diagram                | 2-5  |

|      | 2-4  | Schematic - A1 RF Amplifier                 | 2-9  |

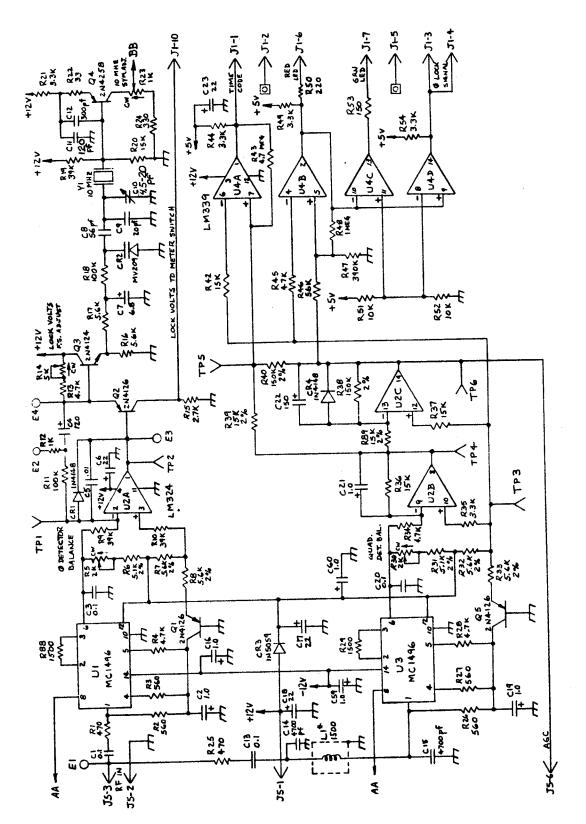

|      | 2-5  | Schematic - A2 Receiver - Sheet 1           | 2-10 |

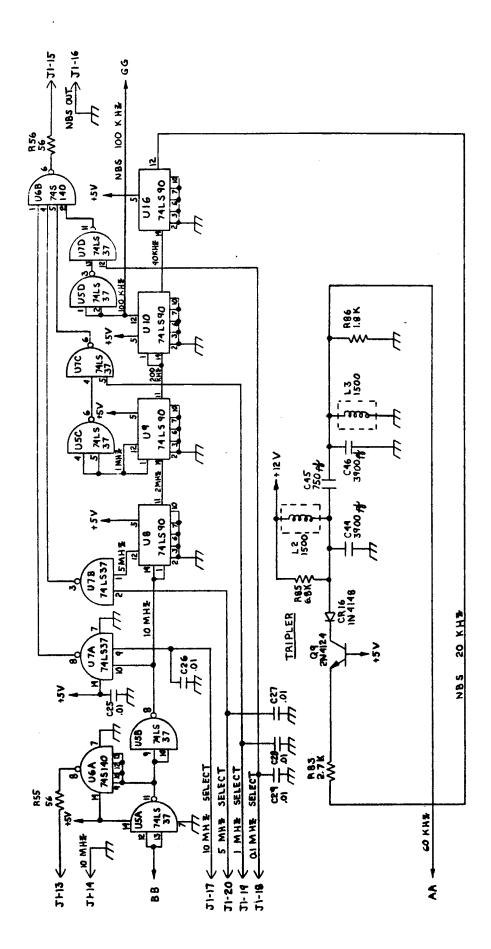

|      |      | - Sheet 2                                   | 2-11 |

|      |      | - Sheet 3                                   | 2-12 |

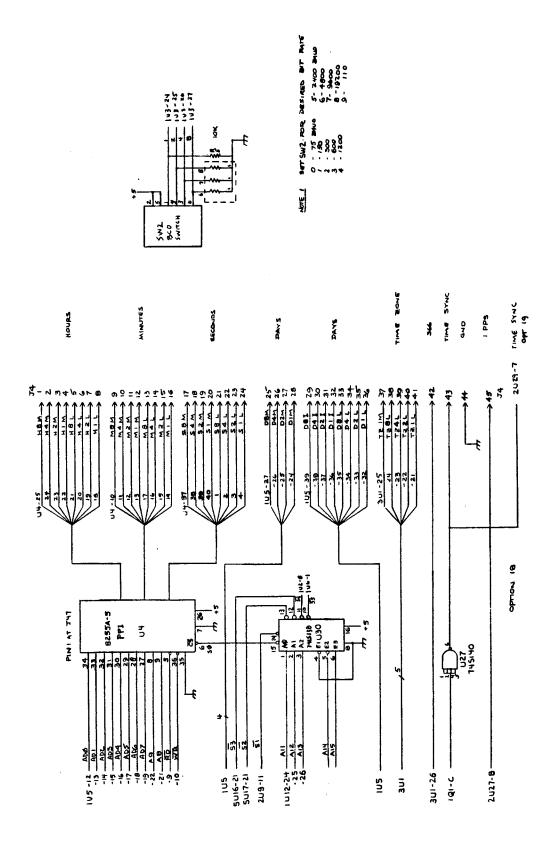

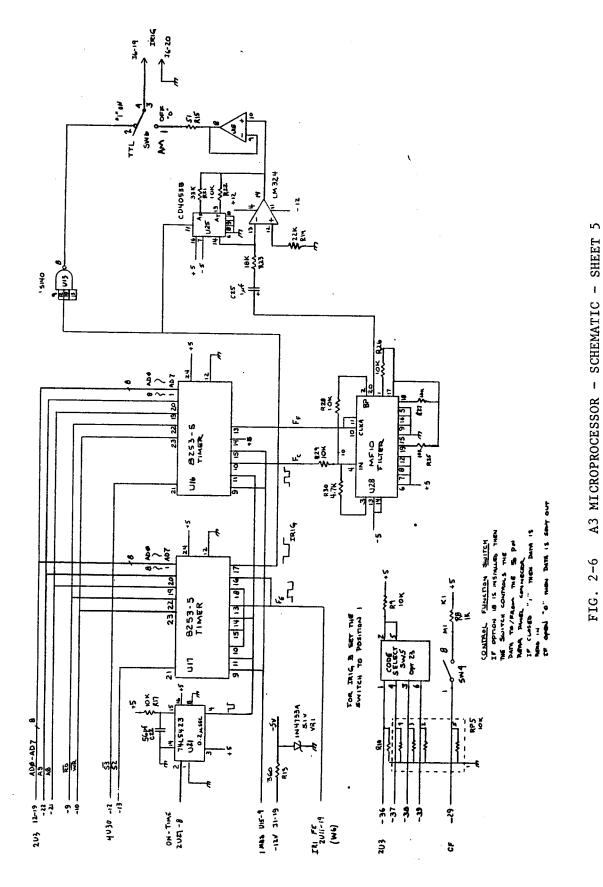

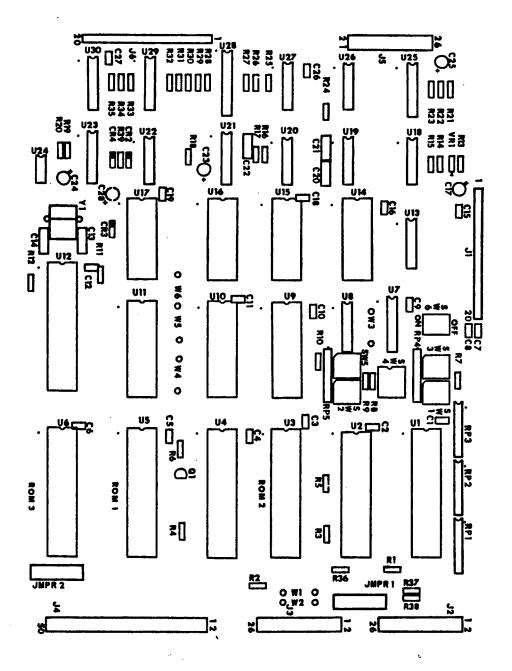

|      | 2-6  | Schematic - A3 Microprocessor - Sheet 1     | 2-15 |

|      |      | - Sheet 2                                   | 2-16 |

|      |      | - Sheet 3                                   | 2-17 |

|      |      | - Sheet 4                                   | 2-18 |

|      |      | - Sheet 5                                   | 2-19 |

|      |      | - Sheet 6                                   | 2-20 |

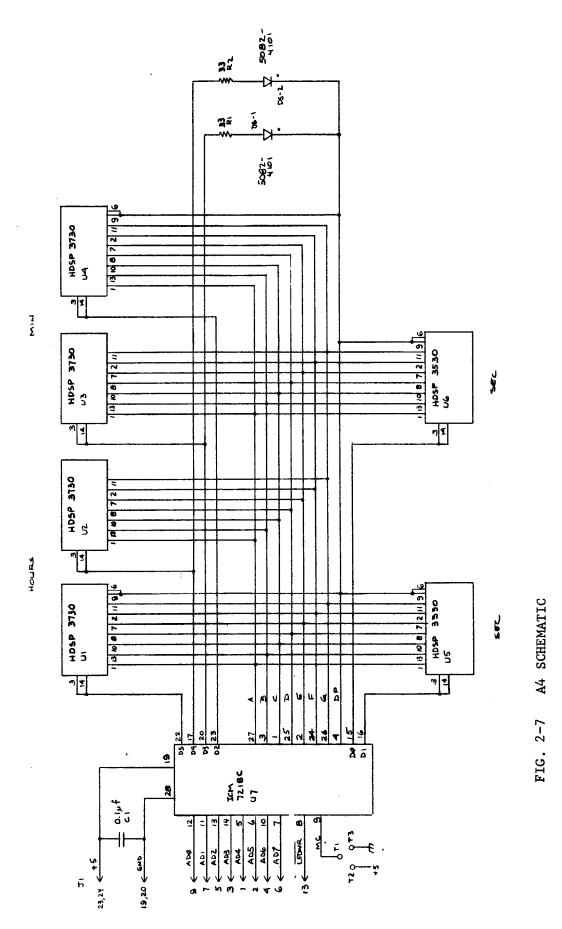

|      | 2-7  | Schematic - A4 Display                      | 2-22 |

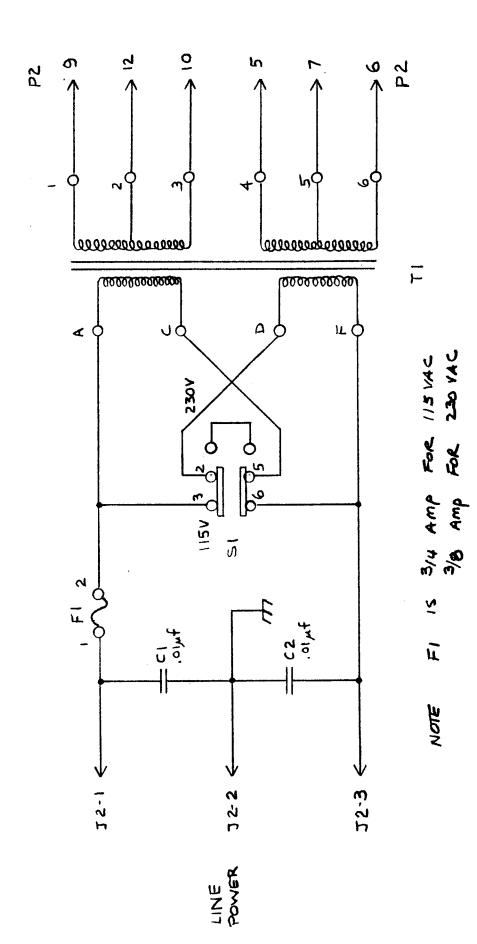

|      | 2-8  | Schematic - AC Power                        | 2-23 |

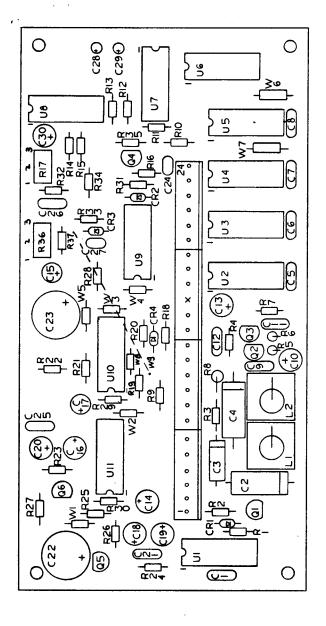

| FIG. | 3-1  | Assembly Drawing - Mainframe                | 3-3  |

|      | 3-2  | Assembly Drawing - RF Amplifier - A1        | 3-4  |

|      | 3-3  | Assembly Drawing - Receiver - A2            | 3-7  |

|      | 3-4  | Antenna Model 8206 Test Setup               | 3-9  |

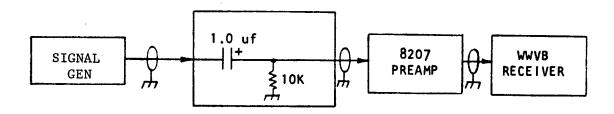

|      | 3-5  | Antenna Preamp Alignment Setup              | 3-10 |

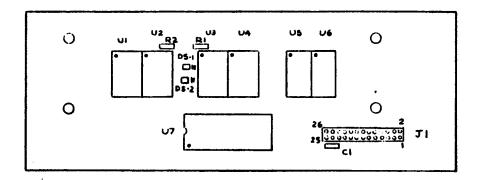

|      | 3-6  | Assembly Drawing - Display A4               | 3-13 |

|      | 3-7  | Assembly Drawing - Microprocessor - A3      | 3-14 |

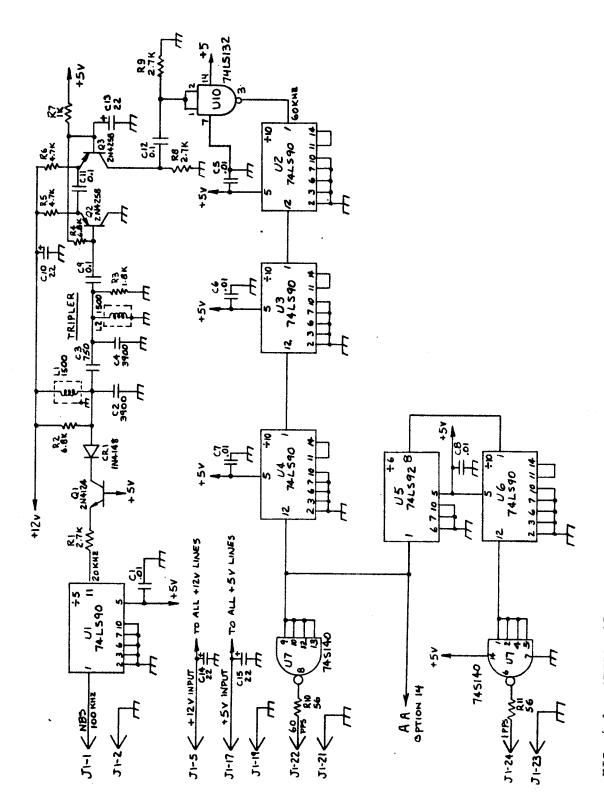

| FIG. |      | Option 15 Schematic                         | 4-3  |

|      | 4-2  | Option 15 Assembly Drawing                  | 4-4  |

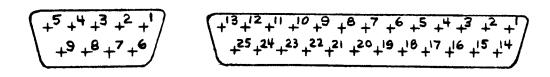

|      | 4-3  | Remote Connector and Serial ASCII Connector | 4-9  |

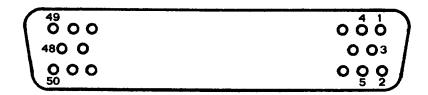

|      | 4-4  | 50-pin Series D Receptacle                  | 4-14 |

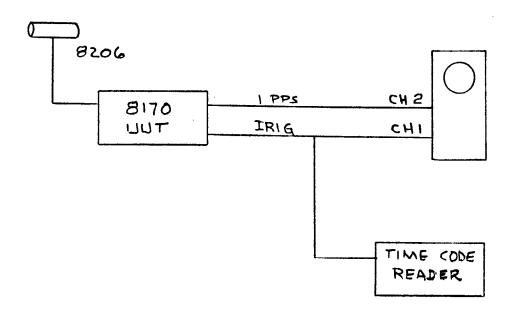

|      | 4-5  | IRIG Test Set-Up                            | 4-18 |

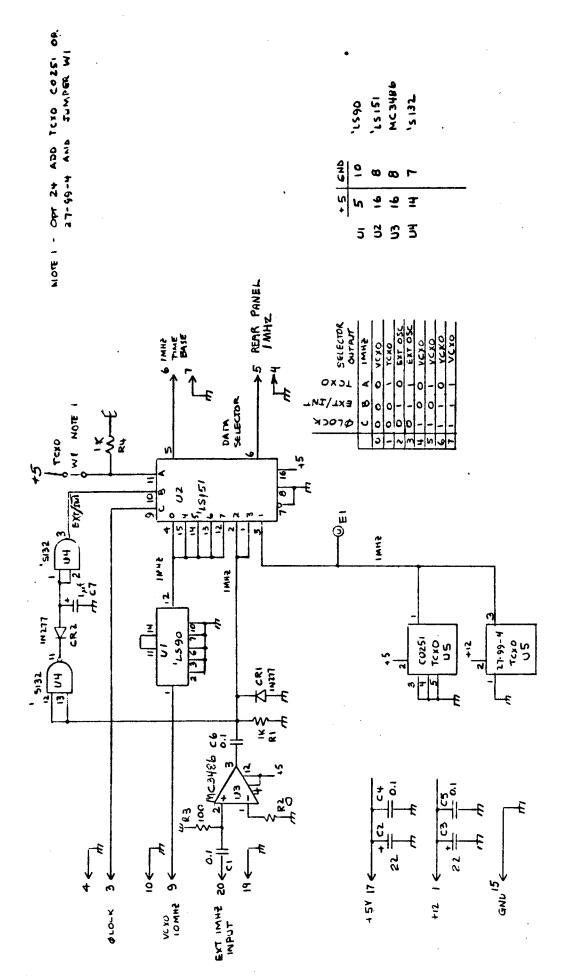

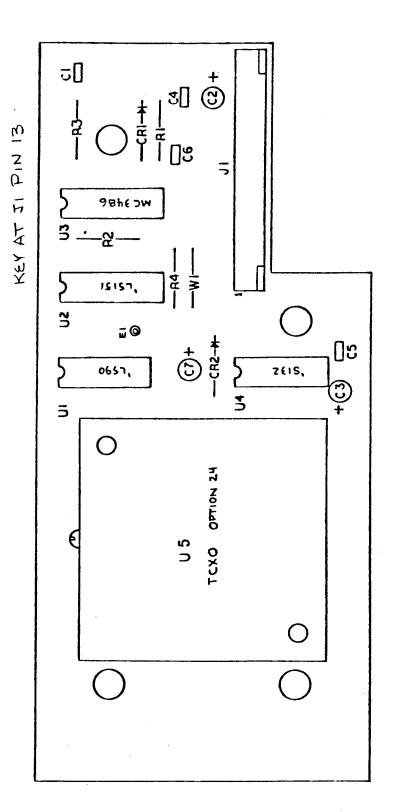

|      | 4-6  | Option 24/25 Schematic                      | 4-22 |

|      | 4-7  | Option 24/25 Assembly Drawing               | 4-23 |

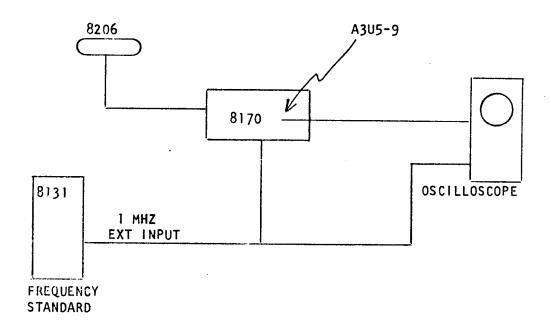

|      | 4-8  | Option 24 and 25 Test Set-Up                | 4-25 |

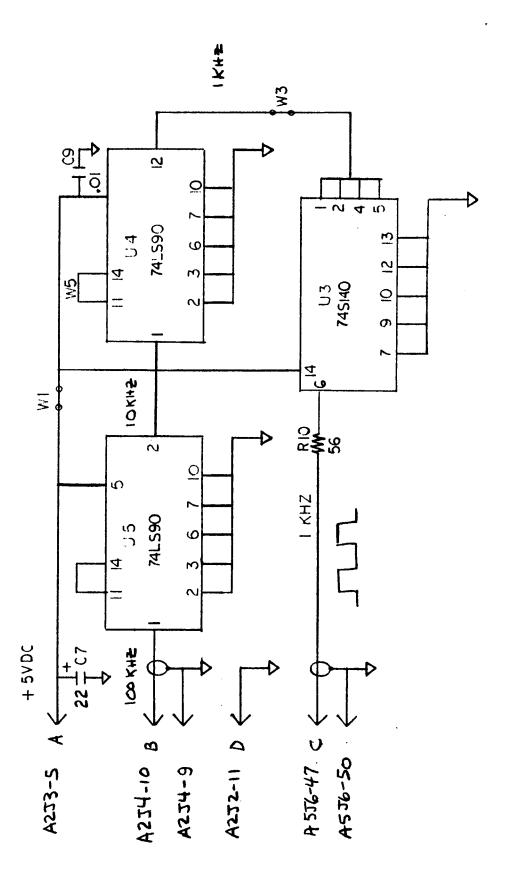

|      | 4-9  | Option 28 Schematic                         | 4-28 |

|      | 4-10 | Ontion 28 Assembly Drawing                  | 4-29 |

# SECTION 1

8170

INSTALLATION & OPERATION

#### 1.1 INTRODUCTION

The Spectracom Model 8170 NBS-Synchronized Clock is a WWVB receiver that decodes the time code signal and provides a front panel display of hours, minutes, and seconds. A serial RS-232C interface provides on command, day of the year, hours, minutes, seconds, time zone and status information. A 1.0-MHz signal phase locked to the WWVB carrier is provided on the rear panel along with a 1-Hz on-time pulse that signals the beginning of each second. A thumbwheel switch on the rear panel provides for time zone and path delay corrections.

## 1.2. INSTALLATION

#### 1.2.1 UNPACKING

In the event of damage to the shipping carton or if there is hidden damage to the equipment, but the carton is not damaged, be sure to contact the carrier immediately so that his representative can witness any equipment damage that may exist inside the carton. If you fail to report shipping damage immediately you may forfeit any claim against the carrier. You should also notify SPECTRACOM CORPORATION of shipping damages so that we can assist you in obtaining a replacement or to repair the equipment.

Be sure to remove all items of equipment and accessories from the shipping carton before discarding it. This includes a three-conductor line cord and an instruction manual.

# 1.2.2 RESHIPMENT

If it is necessary to return the unit to the factory, the original shipping carton may be used. If it is not available, a carton of at least 250# test corrugated paper with at least two inches of polyethylene foam surrounding the unit must be used. The unit should be sealed in a plastic bag for moisture protection and a note must be included stating the reason for the return.

# 1.2.3 ANTENNA LOCATION

The antenna should be mounted a minimum of 25 feet from the receiver to prevent regeneration. The antenna MUST NOT be positioned next to the receiver or on top of it, making the results obtained with the equipment meaningless even though the green LOCK lamp on the receiver front panel may be lit.

The antenna must be as least three feet from any steel beams, roof decking, pipes, etc., as metal will detune the antenna and can cause as much as 20 dB degradation of the signal-to-noise ratio. The antenna must not be mounted under a metal roof or inside a building with heavy steel structural supports, as these shield the antenna from

the signal. Roof tops are generally good if a clear shot toward Fort Collins is available without being blocked by a large steel structure. Attics are ideal sites if the roof and rafters are not metallic. The signal-to-noise ratio will be optimized if the antenna is located as far as possible from local RF noise sources such as large electric motors, power lines, oscilloscopes, TV sets, or fluorescent or neon lamps that blink or sputter on and off. Any equipment containing a switching power supply is a probable cause of interference.

#### 1.2.4 ANTENNA INSTALLATION

The antenna should be mounted where it will not be disturbed, supported by a non-metallic pipe such as a one-inch PVC water pipe. Holding the antenna two or three feet off the ground or rooftop is adequate in most cases. The tubular housing must be positioned broadside to Fort Collins, Colorado, where the transmitter is located (see Fig. 1-1, 1-2, 1-3), and horizontal to the ground, to allow maximum signal reception. No signal will be received if the tube points directly toward the transmitter site, as the antenna pattern nulls are located off the ends of the tube. The antenna position may be optimized using the signal strength measurement described in 1.3.3 SIGNAL STRENGTH.

When the lead-in coaxial cable (RG-58/U is recommended) is connected from the BNC connector on the antenna to the BNC conector on the receiver the system is ready for use, if the antenna has been installed and aimed properly. The antenna has a built-in preamplifier inside its housing that receives its DC operating voltage through the coaxial cable, therefore both the center conductor and the shield of the cable must be continuous from the antenna to the receiver. A short circuit in this line will not harm the equipment as the power supply is adequately protected.

## 1.2.5 INPUT POWER

The equipment may be operated from either 115 or 230 VAC ±10%, 60-Hz line power. A slide switch on the rear panel selects either of the two line voltages. The receiver is shipped with the switch in the 115 VAC position, unless a tag is attached stating otherwise. If the line voltage switch is moved to select 230 VAC, the fuse must be changed also, as indicated on the rear panel. Before turning on the equipment after unpacking, make sure that this switch is in the correct position.

TO AIM ANTENNA AT FORT COLLINS, COLORADO, DETERMINE COMPASS HEADING FROM THIS MAP.

Draw a straight line from the receiver location through Fort Collins, Colo. at the center of the map. Continue until the line intersects the outer ring. The point at which the line intersects the outer ring indicates the compass heading for Fort Collins from your location.

FIG. 1-1 GREAT CIRCLE MAP CENTERED ON FORT COLLINS, COLORADO

FIG. 1-2 ANTENNA MOUNT MODEL 8211

FIG. 1-3 SIGNAL STRENGTH MAP

### 1.2.6 OPERATING ENVIRONMENT

The equipment is designed for operation in a room temperature laboratory environment. Operation outside a temperature range of 0 to 50°C may cause malfunction or damage to the equipment.

#### 1.2.7 BENCH OPERATION

The instrument is provided with four feet for standing on a benchtop surface, along with a tilt stand which may be used to provide a convenient viewing angle.

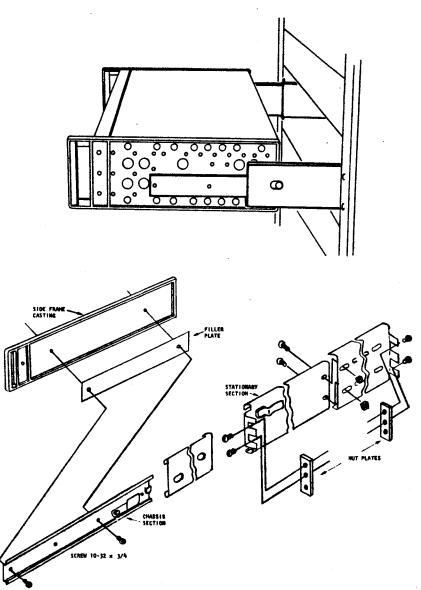

# 1.2.8 RACK MOUNT KIT (Option 01)

Units purchased with the rack mount kit are not provided with the tilt stand. The four mounting feet are included but these may be removed when the receiver is installed in a rack.

The rack mount panel extensions are installed by removing the vinyl-covered filler panels located just behind the handles on the sides of the enclosure. The rack mounting brackets are installed using the oval head  $\#10-32 \times 3/8$  screws provided. Truss head  $\#10-32 \times 3/8$  screws are furnished to mount the unit to the rack. (See Figure 1-4)

# 1.2.9 RACK MOUNT WITH SLIDES (Option 11)

The chassis section of the slides are attached to the sides of the receiver using the  $\#10-32 \times 3/4$  screws provided. The filler plates are located between the slides and the receiver sides.

The stationary section of each rack slide must be assembled to the proper length for the rack being used, using the brackets, screws, and nuts provided. The slides are bolted to the front and rear channels of the rack using the  $\#10-32 \times 1/2$  screws and nut plates as shown in Figure 1-5. Additional panel mounting angles (such as Emcor No. PMA) may be added to the rack cabinet for securing the front ends of the stationary slide sections if needed. They should be located immediately behind the panel mounting angles to which the equipment panel extensions will be fastened.

FIG. 1-4 RACK MOUNT OPTION 01

FIG. 1-5 RACK MOUNT WITH SLIDES (OPTION 11) 1-7

#### 1.2.10 SELECTABLE BIT RATE

Switch (SW2) located on the microprocessor assembly A3 is a 10-position switch which controls the bit rate of the serial I/O port. The table below lists the bit rate as a function of the switch setting.

| Switch Position | Bit Rate |

|-----------------|----------|

| 0               | 75       |

| 1               | 150      |

| 2               | 300      |

| 3               | 600      |

| 4               | 1200     |

| 5               | 2400     |

| 6               | 4800     |

| 7               | 9600     |

| 8               | 19200    |

| 9               | 110      |

|                 |          |

# 1.2.11 PREAMPLIFIER (Model 8207) INSTALLATION

The Spectracom Model 8207 Preamplifier is a low noise, tuned, 60 KHz line amplifier used in the antenna feed line wherever the WWVB signal strength is less than 50 uV/meter at the Model 8206 Loop Antenna or less than 0.3 uV at the receiver antenna terminal. Typical locations where the Preamplifier is probably required are Hawaii, Alaska, Puerto Rico, and the Canal Zone. The Model 8207 Preamplifier provides approximately 40 dB of gain between the antenna and receiver increasing sensitivity to 3.0 nanovolts.

The Preamplifier is connected in the antenna feed line with input connected to the antenna and output connected to the receiver. Because of the high gain of the system, it is recommended that the preamplifier be located at least 10 feet away from the receiver, perhaps where the antenna line enters the room from where the receiver is located. The antenna must be at least 25 feet beyond the Preamplifier from the Receiver. Switch AlS1 of the receiver RF Amplifier must be set at its right-hand position, marked PREAMP or P, prior to equipment turn-on, to apply DC voltage to the Model 8207 on the antenna feed line. If the preamplifier is removed from the system, the switch must be placed in the left-hand position, marked ANT or A prior to turn-on.

It is strongly recommended that no internal adjustment of the Preamplifier be made without consulting the factory.

### 1.2.12 MATING CONNECTORS

The mating connectors for the Remote Output, Parallel BCD, and RS-232C connectors on the rear panel are listed below.

|                                         |                                                                 | SPECTRACOM                  | MFR.                                         |                                    |

|-----------------------------------------|-----------------------------------------------------------------|-----------------------------|----------------------------------------------|------------------------------------|

| REFERENCE                               | DESIGNATION                                                     | PART NO.                    | PART NO.                                     | MFR                                |

| Remote Output<br>(Option 19)            | Plug, 9 position<br>*Socket Pins<br>Shell                       | J03309<br>P004001<br>H52090 | 205204-1<br>1-66505-0<br>206478-1            | AMP<br>AMP<br>AMP                  |

| Parallel BCD (Round Cable) (Flat Cable) | Plug, 50 position<br>*Socket Pins<br>Shell<br>Plug, 50 position | P004001<br>H52500           | 205212-1<br>1-66505-0<br>206478-5<br>609-50P | AMP<br>AMP<br>AMP<br>T&B<br>ANSLEY |

| RS-232C                                 | Plug, 25 position<br>*Socket Pins<br>Shell                      | J03325<br>P004001<br>H52250 | 205208-1<br>1-66505-0<br>206478-3            | AMP<br>AMP<br>AMP                  |

<sup>\*</sup> The crimping tool for the pins is AMP 90302-1. The insertion/extractor tool is AMP 91067-2.

# 1.3 OPERATION

## 1.3.1 FRONT PANEL FUNCTIONS

Unlock/Lock Lamps: The red UNLOCK lamp is lit when there is insufficient signal received for the receiver to lock to the WWVB carrier. This is usually due to improper placement or aiming of the antenna. The green LOCK lamp lights when the receiver acquires phase lock.

Time Sync: The green lamp is turned on when the time code is fully decoded. In order to select the length of time before the time sync lamp goes out after loss of phase lock, switch (SW4-3,4) can be set to select 1 of 4 times:

| SW4-4   | SW4-3   | Typica1    |              |

|---------|---------|------------|--------------|

| Setting | Setting | Time (min) | Error (msec) |

| 0       | . 0     | 10         | 1            |

| 0       | 1       | 20         | 10           |

| 1       | 0       | 60         | 30           |

| 1       | 1       | 180        | 100          |

The lamp will come back on after the receiver reacquires phase lock to the WWVB carrier and the time code is decoded.

If high accuracy during loss of signal is required then Option 24/25, TCXO and External Oscillator is recommended. Refer to Section 4 Options for details.

Display: The display initially indicates time since "power on" in the four right hand digits. After phase lock is achieved the sixth digit displays the code received. A zero (0) is a logical zero, a one (1) is a logical one, a two (2) is a position identifier and a four (4) indicates a bit error. After the code is successfully received universal coordinated time (UTC) minus the time zone switch setting is displayed.

#### 1.3.2 REAR PANEL FUNCTIONS

Thumbwheel Switch: This is a 5-digit switch. The right two digits are TIME ZONE. The left three digits are PROPAGATION DELAY and RECEIVER DELAY inputs. The propagation delay can be calculated (see Section 1.3.9 PROPAGATION PATH DELAY). The receiver delay is a nominal 17 milliseconds. Set the switch to the sum of the path delay and receiver delay.

Daylight Savings Time: Use the TIME ZONE switch to adjust the display for local time.

Parallel BCD: Option 18 provides the day of the year, hours, minutes, seconds, time zone and status data on a 50-pin series D socket.

Remote Output Driver: Option 19 provides a RS-422 serial data output for driving Model 8172 Synchronized Wall Clocks or Model 8173 Multiple RS-232C Taps.

IRIG B Output: Option 23 provides 1-KHz carrier, amplitude modulated at 100 pps with time code or 100 pps DC level shift.

External Oscillator Input: Option 24 or 25, rear panel BNC input for 1.0-MHz standby clock oscillator.

1 KHz Output - Option 28, provides a 1-KHz signal phase locked to WWVB carrier. Brought out on pin 47 of 50-pin series D connector. Pin 50 is ground return.

Serial ASCII: This interface is a serial RS-232C port. The connector is a 25-pin series D socket.

There are 3 commands:

S - Set the clock

T - Read the time

D - Dump the memory

1 MHz: 1.0 MHz phase locked output. TTL compatible (SN74S140 source).

1 PPS ON-TIME: 1 pulse per second. TTL compatible (SN74S140 source). The leading edge is synchronized to the WWVB reduction of the carrier level that occurs at the beginning of every second.

Power: International Electrotechnical Commission (IECS) male line cord receptacle.

Line Fuse: AC line fuse. 3/4 ampere for 115 VAC operation and 3/8 ampere for 230 VAC operation.

Line Switch: Line switch to allow operation with 115 volt or 230 volt primary AC source.

Antenna: BNC connector for WWVB antenna.

### 1.3.3 SIGNAL STRENGTH

The Spectracom receiver may be used to measure relative field strength of the 60 KHz signal. This measurement may be used to optimize reception by indicating the best location and orientation of the antenna.

The WWVB receiver employs synchronous AGC which responds to the 60-KHz signal only and is not affected by noise. The AGC level, therefore, provides an excellent indication of signal strength.

To measure this AGC voltage, open the cover of the receiver and locate test points TP3 and TP6 on the Receiver board, A2. Place the positive lead of a DC voltmeter on TP6 (blue) and the negative lead on TP3 (orange). The input impedance of the voltmeter should be greater than 10 megohm. The voltage will be approximately 2.0 VDC at a field strength of 100 microvolts/meter using a properly oriented Model 8206 antenna. The AGC voltage will increase in strong signal locations, rising to a limiting value of approximately +3.6 volts as the frontend input signal level increases.

As the signal strength decreases to the receiver phase lock threshold of about 0.2 microvolts, the AGC voltage decreases to about +1.0 VDC. The red UNLOCK panel lamp will light below this level. The AGC voltage will decrease to a varying level around zero if the input signal is removed completely. As the signal is reapplied and increased, the receiver will again lock at an AGC level of approximately 1.0 volt.

The relative signal strength measurement may be used to aid antenna orientation by placing the antenna to maximize the AGC voltage measurement. The circuit that develops the AGC voltage has a very long time constant, so that a pause of 30 to 60 seconds is necessary

after each move of the antenna to allow the AGC to stabilize at the new level. A few minutes of experimentation should produce good antenna orientation.

### 1.3.4 INTERNAL SWITCHES

There are four, ten-pole BCD switch assemblies on the A3 Micro-processor board (014801).

The general purpose of these switches are as follows:

A3SW1 - Units-year select for option 30

A3SW2 - Selectable bit rate

A3SW3 - Tens-year select for option 30

A3SW5 - Code select switch - Position 1 selects IRIG B code. The remaining switches are reserved for future code options.

There is also a four-positon dip switch (A3SW4) and a one-position dip switch (A3SW6) on the A3 board.

The functions of these switches are as follows:

A3SW4 - The CF switch (SW4-1) controls data to/from the rear panel parallel BCD connector. This switch is functional when IRIG B Option 23 and Parallel BCD Option 18 are present. SW4-2 is the Option 30 select switch. SW4-3,4 controls Time Sync LED. See SW4 functions below.

A3SW6 - TTL/AM switch selects a TTL or amplitude modulated 1 KHz signal for the IRIG output.

The internal switches are set as indicated below when the unit is shipped from the factory, provided its corresponding option is present.

```

A3SW1 - Present Unit's Year (Option 30)

SW2 - 2 (300 Baud)

SW3 - Present Ten's Year (Option 30)

SW4-1 - OFF (Option 18/23)

-2 - OFF (Option 30 Enable)

-3,4 - ON, ON (Time Sync Indicator)

SW5 - 1 (Option 23)

SW6 - ON (Option 23)

```

If Option 23 is not available, SW5 and SW6 will not be on the board and SW4-1 will be non-functional.

The functions of SW2 and SW4 are listed below:

SW2 - 0 75 Baud Rate 1 150 300 2 3 600 4 1200 5 2400 6 4800 7 9600 19200 8 9 110

- SW4 1 Control Function for Option 18/23 ON - Data read into 8170 OFF - Parallel BCD time of year data is from 8170

- 2 Option 30 Select

OFF STD output

ON Option 30 Fully Decoded Text Stream

SW4-3,4 Time Sync LED Indicator: See Table Below

| <u>4</u> | <u>3</u> | TIME (min) | ERROR (msec) |

|----------|----------|------------|--------------|

| 0        | 0        | 10         | 1            |

| 0        | 1        | 20         | 10           |

| 1        | 0        | 60         |              |

| 1        | 1        |            | 30           |

| 1        | 1        | 180        | 100          |

|          |          |            |              |

( 0 = OFF; 1 - ON)

### 1.3.5 INITIAL TURN-ON

After the receiver and antenna have been installed, plug the receiver into the power line, after making sure that the rear panel slide switch is in the correct position for the line voltage. Note that the green LOCK lamp lights within one minute. If the red UNLOCK lamp stays lit, insufficient signal is being received, probably due to improper antenna placement or alignment. The time since turn-on is displayed in minutes and seconds. The time code received is displayed in the left digit.

The time code display is coded:

- 0 binary zero

- 1 binary one

- 2 position identifier

- 4 bit error

The clock receives the code and sets itself automatically. The time it takes to set is dependent on the quality of the signal received. The quality of the signal is indicated by the code received. If many 4's are displayed, then the signal is poor. If the

signal is good, then the clock will set in a few minutes. If there is a weak or noisy signal, it will take longer to set.

### 1.3.6 COMMANDS

Commands are accepted through the Serial ASCII port. Commands are:

- T print the Time

- S Set the time

- D Dump the memory

Serial Data Interface:

RS-232 Port: Standard in all units, provides day and time in response to a T input command. S command allows operator to set clock via a data terminal keyboard. D command causes a memory dump of statistical data for performance evaluation. A character consists of 1 start, 8 data, and 2 stop bits. Data rate is selectable from 300 to 19,200 baud.

Serial Data Structure: Response to a T command is:

(CR) (LF) I (SPACE) (SPACE) DDD (SPACE) HH: MM: SS (SPACE) (SPACE) TZ=XX (CR) (LF)

#### where:

I = space if clock set by WWVB (TIME SYNC lamp on)

- \* if clock set manually via RS-232 port

- ? if time sync lamp is off

DDD = day of the year

HH:MM:SS = hours:minutes:seconds

XX = time zone switch setting at rear panel

Output is in UTC minus the time zone switch setting.

Option 30 Fully Decoded Text Stream: This alternate data format can be furnished when the unit is purchased:

(CR)(LF)I(SPACE)WWW(SPACE)DDMMMYY(SPACE)HH:MM:SS(CR)(LF)

where: I = as defined above

WWW =day of week (MON, TUE, WED, etc.)

DD = numeric day of month (1 to 31, leading zero suppressed)

MMM = month (JAN, FEB, MAR, APR, etc.)

YY = year without century (83, 84, 85, etc.)

HH:MM:SS = as defined above.

"S" Command - to manually set the clock, enter:

#### SDDDHHMMSS

where: S = set command

DDD = UTC day of year

HH = UTC hours

MM = minutes

SS = seconds

Entry of the last seconds digit sets the clock to UTC time minus the time zone switch settings. The WWVB-derived on-time pulse increments the clock every second. If phase lock to the carrier has been acquired, the on-time second pulses are phase locked to the time code pulses even though the unit may temporarily be unable to decode the incoming signal. Thus, if the manual setting started the clock within one second after the correct on-time pulse, it will run truly on-time, as though it had set itself.

If Option 30 is present and the operator enters 366 for DDD day and the internal year switch is not set to a leap year, then the error message "\*CHK YEAR SW" will be printed.

"D" Command - the "dump the memory" command, will print the contents of the 256-byte RAM memory. Performance event counters stored in RAM are:

Phase Lock Lost Counter PLLC Time Code Compare Counter TCCC

The print out represents physical address locations 0800 through 08FF. The data is printed in hexadecimal notation. PLLC is a two-byte counter whose contents are printed at row 0810, columns 8 and 9. The first byte is the least significant byte. The counter records the number of times phase lock has been lost since power-on.

The Time Code Compare Counter, TCCC, records the number of times the received data compares with the expected value. It is printed at row 0820, columns 8 and 9. It is a 2-byte hexadecimal number printed least significant byte first.

Figure 1-6 is the print-out from a sample dump command.

### 1.3.7 PHASE ADJUST TABLE

The 1 PPS on-time pulse is phase locked to the leading edge of the received time code signal. After the initial turn-on sequence the phase adjustments are in 0.1 millisecond increments. Each time an adjustment is made the time and direction of the adjustment are logged in a circular table. The table is located at 08AO through 08DE. The table contains the data on the last 21 phase adjustments. UTC hours and minutes followed by 00 or FF are logged, where 00 indicates the 1

PPS was shifted 0.1 millisecond left (early) and FF indicates that the 1 PPS was shifted 0.1 millisecond right (late). The current position pointer is located at row 0800, columns D and E, least significant byte first. This points to the memory location where the next adjustment will be stored.

After the unit has been on a few days the adjustment interval will exceed 24 hours. If adjustment data is desired the memory should be dumped at least once every 24 hours. This eliminates ambiguity concerning which day the adjustment was made.

#### 1.3.8 TIME FLAGS

At power-on or after the signal has been lost for longer than 60 minutes (depending on SW4-3,4) the Time Sync light will be off. This indicates that the time may be in error by greater than 30 milliseconds. If high accuracy during loss of signal is required, then Option 24/25, TCXO and External oscillator is recommended. See Section 4 Options for details. The Time Sync light is turned on when a good time code is received. A received time code must pass a number of tests. When the seconds, minutes, hours and days portion of the time code are acceptable, flags are set to FF at row 0880, columns 8 through C. The clock is set and the Time Sync light is turned on when all the flags are set. This data is useful during the initial installation and trouble shooting to determine the progress of the self-setting process.

Once the Time Sync light is on the clock will keep UTC time. The display will be changed when 3 consecutive good compares are received that do not agree with the display data. This will happen when the leap second is inserted.

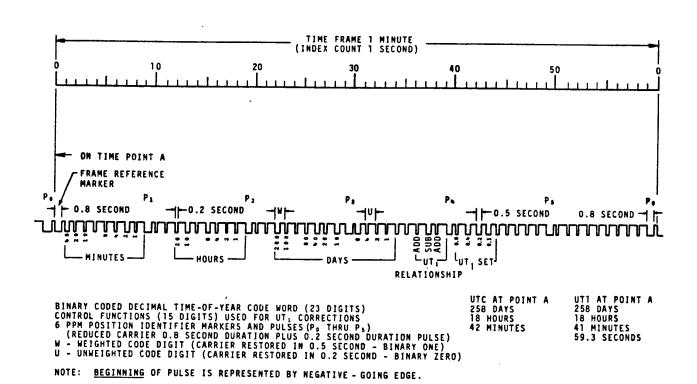

### 1.3.9 TIME CODE FORMAT

The WWVB time code is generated at the transmitter by a reduction of the carrier power of 10 dB at the beginning of each second. It is restored to a full power 200 milliseconds later for a binary zero, 500 milliseconds later for a binary one, and 800 milliseconds later for a position identifier. Decoding a one-minute data stream yields day of the year, time of day, and a correction factor for converting from atomic time (Coordinated Universal time, UTC) to earth time (UTI). Figure 1-7 WWVB TIME CODE FORMAT shows the coded data in a 1-minute time frame.

```

PLLC

TCCC

Pointer to phase

9 A B

/ C

D E

adjust table

48 00 1D 02 DO E9 F4 00 10 00 F 14 43 08 FF

0800

0810

FF 00 01 00 00 F4 00 00 00 45/54 00 FF 00 00

0820

27 28 14 25 05 00 01 99 07 01 00 00 00 99 49

0830

28 14 25 00 00 00 03 01 28 FF 34 48 00 00 00

0840

28

14 02 50 50 00 00 32 28

14 25 05 00 00

0850

20 20 32 35 30 20 31 34 3A 32 38 3A 32

0860

33 20 20 54 5A 3D 30 30 QD 0A 00 0Q 53 48 00 00

0870

0880

80 48 7D 00 UC 44 00 00 FF FF FF FF 00 00 00 00

Time Flags

0890

0880

19 04 FF 22 00 FF 00

15 20 00 15 50 FF

08B0

00 FF 01 53 00 02 15 00 02 46 00 03 13 00 03 54

08co

00 04 48 00 09 51 00 10 39 06 11 12 00 14 39 FF

Phase Adjust Table

0800

17 03 FF 20 35 FF 04 25 00 09 12 00 20 52 FF 00

08E0

00 00 00 00 00 00 00 00 00 03 43 B4 45 EA 47 F2

08F0

41 88 47 00 49 00 00 00 00 54 64 04 41 00 00 00

```

FIG. 1-6 SAMPLE MEMORY DUMP

FIG. 1-7 WWVB TIME CODE FORMAT

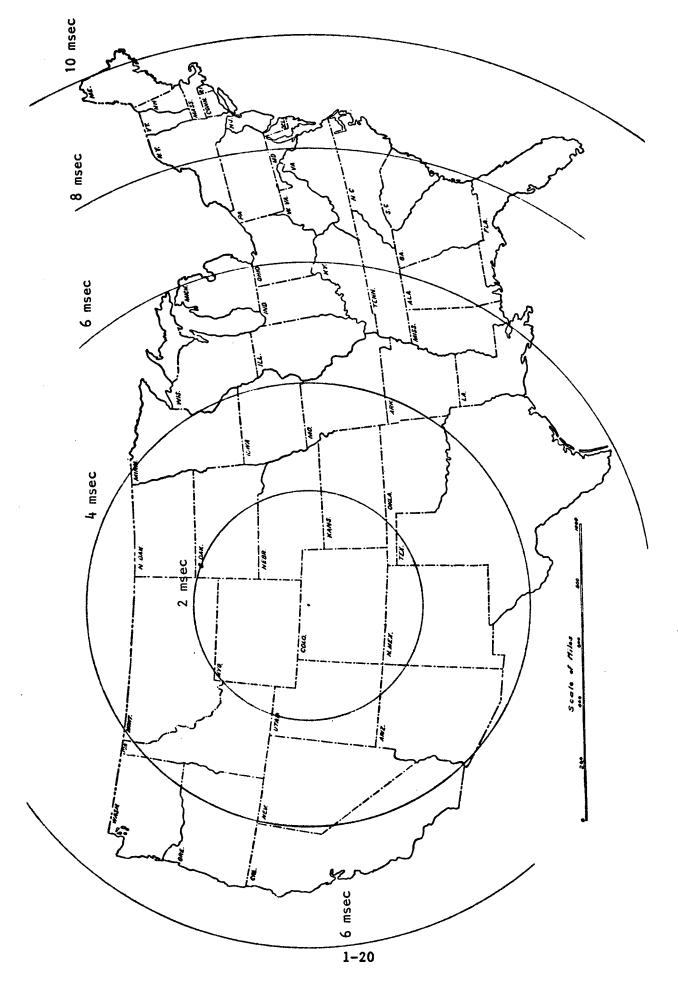

### 1.3.10 PROPAGATION PATH DELAY

Radio waves at low frequencies use the earth and the ionosphere as a waveguide and follow the earth's curvature for long distances. To compute the propagation path delay the great circle distance between the two points is divided by the speed of light.

The approximate formula for finding the great circle distance from Ft. Collins, Colorado, to another point in the northern hemisphere is given below. The error is 2% or less.

The Great Circle Map shown in Figure 1-1 may be used to determine the approximate receiver location.

Distance =  $60 \cos^{-1}$  (.758 cos (LAT) cos (P) + .652 sin (LAT)) nautical miles.

where: LAT = latitude of receiver

P = Longitude of WWVB minus the longitude of receiver

WWVB is at 10502' 39.5" W longitude

The speed of light is 300 Km/millisecond

To convert from nautical miles to millisecond delay:

PATH DELAY = Nautical Miles x 1.8522 Km/Nautical mile

300 Km/msec

An example of the calculation is given below for Boston:

PATH DELAY = 1521 nautical miles x 1.8522 Km/nautical mile

300 Km/msec

### = 9.4 milliseconds

The path delay from the WWVB transmitter in Ft. Collins, Colorado, to Boston is 9.4 milliseconds.

Figure 1-8 Path Delay Map shows the United States with concentric circles around Ft. Collins, Colorado. The radius of the inner circle is 600 Km and represents a 2 millisecond path delay. Outer circles represent increasing 2 millisecond delays. The map provides only an approximate value for path delay.

Add the calculated path delay to the 17 millisecond receiver delay and enter the sum into the path delay thumbwheel switch.

#### 1.3.11 TIME ZONE SETTINGS

The time zone switch is used to offset UTC time to display and output a local time. Once a time zone is entered the Model 8170 will reflect the local time within one second.

Use the table below to determine time zone settings. Areas that do not observe daylight savings time should enter the standard time value for that time zone.

#### TIME ZONE SETTING

| TIME ZONE | STANDARD TIME<br>(OCTOBER - APRIL) | DAYLIGHT SAVINGS TIME<br>(APRIL - OCTOBER) |

|-----------|------------------------------------|--------------------------------------------|

|           |                                    |                                            |

| ATLANTIC  | 4                                  | 3                                          |

| EASTERN   | 5                                  | 4                                          |

| CENTRAL   | 6                                  | 5                                          |

| MOUNTAIN  | 7                                  | 6                                          |

| PACIFIC   | 8                                  | 7                                          |

| UTC       | 0                                  | 0                                          |

#### TABLE 1-1 TIME ZONE SETTINGS

The time zone switch must be manually updated when changing from standard time to daylight savings time and back to standard time.

## 1.3.12 LEAP YEAR SWITCH

The 365/366 toggle switch must be placed in the 366 position during leap years. This allows the receiver to automatically convert day-of-year properly to month and day during leap years. This also allows receivers that convert UTC time to local time to "back up" properly to either day 365 or 366 as appropriate upon change of year.

#### 1.3.13 SPECIFICATIONS

## RECEIVER:

Received Standard Frequency: 60 KHz NBS Station WWVB

Sensitivity: 0.4 uV rms into 50 ohms. Minimum field strength at antenna, 25 uV per meter when used with Model 8206 Antenna. 40 dB additional gain may be obtained using Model 8207 Preamplifier in remote locations such as Hawaii, Puerto Rico, Panama, and Alaska.

Receiver Delay: nominal 17 milliseconds. The precise calibration of receiver delay and propagation delay may be made with a portable clock.

FIG. 1-8 PATH DELAY MAP

Phase Lock Indication: Red/Green UNLOCK and LOCK lamps on front panel show synchronous detection of WWVB carrier signal.

#### SIGNAL OUTPUTS

1 MHz: Standard frequency output phase locked to WWVB carrier. A 3.4 volt TTL compatible square wave into an open circuit. A 2.0 volt square wave into 100 ohms.

1 PPS: A Positive-going "on-time" signal phase locked to the leading edge of the WWVB 10 dB power reduction. A 3.4 volt TTL compatible pulse (10% duty cycle) into an open circuit. A 2.8 volt pulse into 100 ohms.

SERIAL ASCII: An Intel 8251A Programmable Communication Inter face is used to provide the RS-232 informaton. It is programmed for:

- 1 start bit

- 8 bits per character

- 2 stop bits

The Serial ASCII port provides the day and time data in ASCII format. The interface is RS-232C compatible. The connector is a 25-pin series D female connector DB-25S or equivalent. The signal names and pin numbers are listed below:

| SIGNAL                        | MNEMONIC | PIN           |

|-------------------------------|----------|---------------|

| Protective Ground             | AA       | J5 <b>-</b> 1 |

| Transmit Data                 | BA       | J5-2          |

| Receive Data                  | BB       | J5 <b>-</b> 3 |

| Request to Send               | CA       | J5 <b>-</b> 4 |

| Clear to Send                 | СВ       | J5 <b>-</b> 5 |

| Data Set Ready                | CC       | J5-6          |

| Signal Ground                 | AB       | J5 <b>-</b> 7 |

| Received Line Signal Detector | CF       | J5-8          |

The Request to Send and Clear to Send signals are connected together inside the Model 8170. The Received Line Signal Detector and Data Set Ready will be high when power is on. They are connected together and tied to +12 volts through a 5.1K resistor inside the Model 8170.

The time data is sent out in reponse to a "T" command. The data represents the time at the beginning of the first character sent. If Option 30 is present the date will be sent as well as the time data. The baud rate is selected by A3SW2.

Relative to RS-232C definitions, the Model 8170 is a data communication equipment DCE. Transmit Data, BA, is  $\underline{TO}$  the Model 8170. Received Data, BB is  $\underline{FROM}$  the Model 8170.

SELECTABLE BIT RATE The Serial ASCII output is internally switch-selectable to 75, 150, 300, 600, 1200, 2400, 9600, 19,200, and 110 bits per second by switch A3SW2.

#### MECHANICAL & INSTALLATION

Size: 5.25H x 13.5D x 17W (inches). Height is 6 inches including feet. If feet are removed, unit may be mounted in a 5 1/4" rack space.

133 H x 343 D x 432 W (mm). Height is 152mm including feet. Handles protrude 1.75 inches (45mm) from front panel. Allow 2-3 inches cable clearance at rear.

Weight: 15 lbs. (6.7 Kg): Shipping Wt. 18 lbs. (8.2 Kg). Line Power: 115/230 VAC +-10%, 50/60 Hz, 20 VA

Operating Temperature: 0 to 50C.

OPTIONS AND ACCESSORIES AND RELATED UNITS

### Options:

Option 01: Rack Mount Kit

Option 11: Rack Mount with Slides Option 15: Timing Pulse Outputs

Option 18: Parallel BCD

Option 19: Remote Output Driver is now standard on units with S/N 8170-601 and higher.

Option 23: IRIG B Output

Option 24: TCXO

Option 25: External Oscillator Input

Option 28: 1 KHz Output

Option 30: Fully Decoded Text Stream

### Accessories:

Model 8206 Loop Antenna

Model 8207 Line Preamp (60 KHz)

Model 8211 Antenna Mount

## Related Products

Model 8172 Remote Clock

Model 8173 Multiple RS-232 Tap

SECTION 2

8170

THEORY OF OPERATION

# 2.1 INTRODUCTION

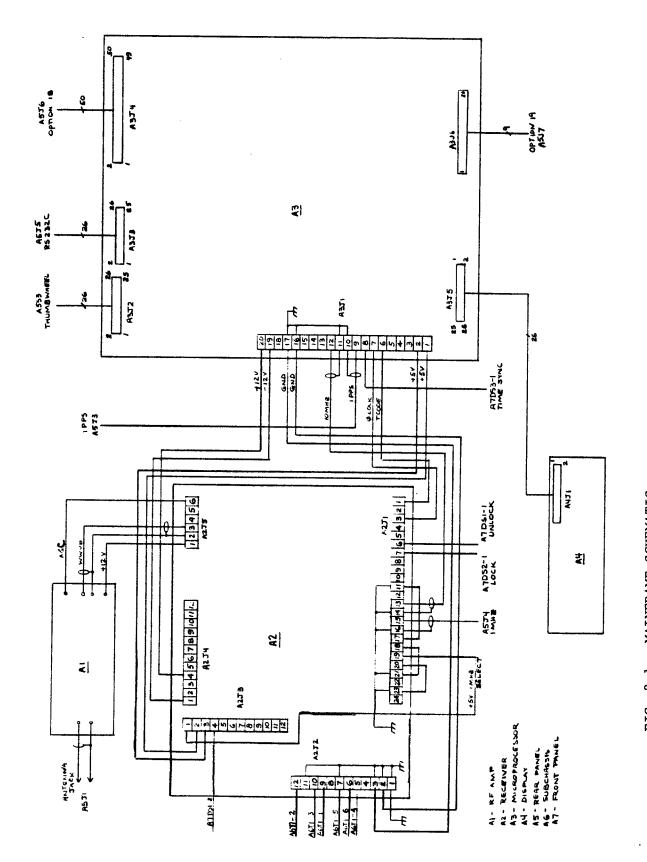

The 8170 consists of an RF Amplifier Assembly, a Receiver Assembly, a Microprocessor Assembly and a Display Assembly as shown in Figure 2-2 Receiver Block Diagram, and Figure 2-3, Microprocessor Block Diagram.

The 60 KHz output of the RF Amplifier is fed to the receiver assembly where the carrier is detected and translated to a phase-locked 10 MHz. This is divided down to provide a 1-MHz NBS phase-locked signal at the rear panel. The AGC voltage is generated in the Receiver Assembly for use in controlling the gain of the RF Amplifier.

The time code information is detected and sent to the Microprocessor Assembly along with the phase lock/unlock condition.

The Microprocessor Assembly consists of an 8085A microprocessor, 6K of EPROM, 512 bytes of RAM, 2 timer chips, a priority interrupt controller, a USART and LED display interface.

The processor integrates out the noise, measures the pulse width, decodes the signal, phase locks a 1-Hz on-time pulse to the received signal, and controls the display and time-of-year outputs.

Input signals from the thumbwheel switch on the rear panel provide time zone and path delay corrections.

# 2.2 MAINFRAME SCHEMATIC

Figure 2-1 Mainframe Schematic shows the interconnection between the various subassemblies. Each of the boards are described in this section.

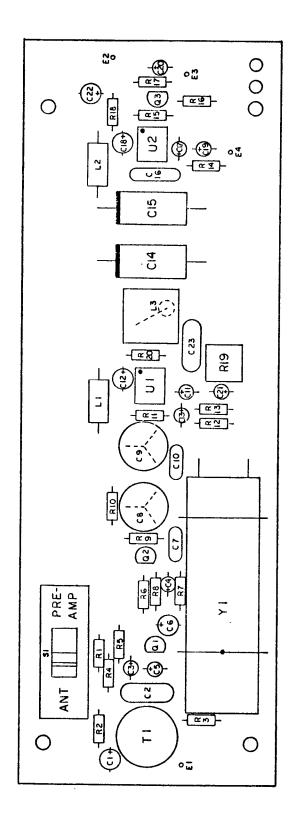

# 2.3 A1, RF AMPLIFIER, P/N 001100

The RF Amplifier assembly filters and amplifies the antenna signal to a level suitable for use by the A2 Receiver Assembly. (See Figure 2-4 for the schematic.)

The signal from the antenna is applied to input transformer T1 which matches the 50-ohm line impedance to the input of the first stage of amplification, Q1. The impedance looking into transformer T1 is approximately 50-ohms, with the secondary of T1 and capacitor C2 forming a 60-KHz tuned circuit with approximately a 200-Hz bandwidth. The output of amplifier Q1 is applied to transistor Q2 which, together with crystal Y1 and capacitors C7, C8, C9 and C10, form a narrow bandpass crystal filter centered at 60 KHz. Capacitors C9 and C10 feed to the output side of the crystal a signal that is 180° out of phase and is tuned so that a passband null occurs at 100 KHz. This combination provides a sharp bandpass response at 60 KHz with very steep high frequency rejection.

FIG. 2-1 MAINFRAME SCHEMATIC

FIG. 2-2 RECEIVER BLOCK DIAGRAM

FIG. 2-3 MICROPROCESSOR BLOCK DIAGRAM

The output from the crystal filter is fed to amplifier U1, whose output is tuned with inductor L3 and capacitors C14, C15, and C23. Amplifier U1 is the stage that provides AGC for the receiver, with its gain control input port at pin 5. Trimmer resistor R19 provides AGC level adjustment.

The output of amplifier stage U1 is fed to the input of the second amplifier stage U2, the output of which goes to emitter follower Q3, providing the output signal to the A2 receiver assembly.

The supply voltage for the RF amplifier is +12 volts fed in at P2-1 and through R18, L2, and L1, to provide power for the amplifier stages. This power supply is also fed through switch S1 and resistor R2 to the input transformer where it goes out onto the antenna line to provide DC voltage to the preamplifier in the antenna. If switch S1 is moved to the P (Preamplifier) from the A (antenna) position the power supply is fed through R1 providing a smaller voltage drop so that both a series line preamplifier Model 8207, and the antenna may be powered from the receiver.

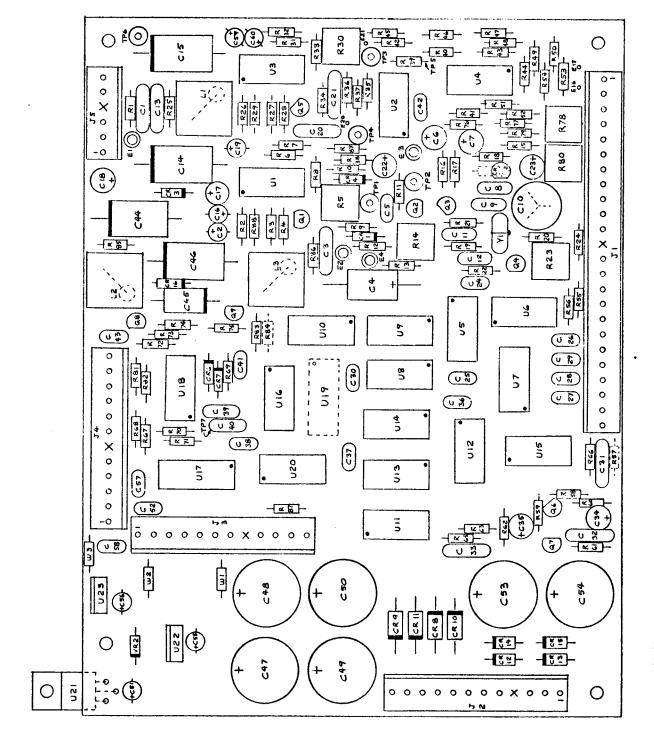

# 2.4 A2, RECEIVER ASSEMBLY, P/N 001200-1

When the signal from the RF amplifier assembly is fed into connector J5-3, it splits and goes in two directions. The first, through U1 and U2A, is the phase locked loop which provides synchronous detection of the carrier frequency and translates it to 10 MHz at the detector output. The second is through U3 and U2B to provide AGC voltage, time code detection, and phase lock/unlock indication.

Other functions of the A2 receiver assembly board include derivation of the rear panel 1-MHz NBS output signal from the 10-MHz phase locked oscillator and the power supplies. See Figure 2-5, sheets 1, 2 and 3.

# 2.4.1 Phase Locked Loop

The reference input to phase detector U1 pin 1 comes from the RF amplifier output (A1 assembly). The comparison frequency input to phase detector U1 pin 8 is derived from the phase locked oscillator, Q4 output. The output from U1 is a DC voltage which is a function of the phase difference of these 60-KHz signals. The output is amplified by U2A, the loop filter/amplifier. This amplified DC voltage is then fed through amplifiers Q2 and Q3 where it becomes the VCO control voltage which pulls the oscillator (Q4 and Y1) into phase lock relationship with the incoming carrier frequency from WWVB. This oscillator pulling is performed by the DC voltage which appears on the upper end of voltage variable capacitor CR2 controlling the "pulling" of crystal Y1. The oscillator output frequency is thus held at exactly 10 MHz by the DC voltage applied to the VCO control line. The

collector output from Q4 at BB is buffered by gate U5A and fed to a divider chain consisting of U8, U9, U10, and U16. A 1-MHz signal is selected and fed to the 1-MHz NBS output connector on the rear panel.

The 20-KHz output from U16 is fed to U18D and to the tripler stage Q9 where the output at 60 KHz is filtered and fed back at point AA into the comparison input of phase detector U1 pin 8. Thus, the phase locked loop translates the incoming 60-KHz carrier frequency from WWVB to 10 MHz at the crystal oscillator output, and divides it down to 60 KHz for comparison in the phase detector.

### 2.4.2 AGC Loop

The input from the RF amplifier also goes to pin 1 of phase detector U3 after being shifted in phase by 90° by C14, C15, and L1. Thus, U3 becomes a quadrature phase detector whose output at pin 6 goes high only when the inputs at pin 1 and pin 8 are in quadrature with each other at 60 KHz. The output level from this phase detector is proportional to the level of the incoming carrier, and thus provides the basis for time code amplitude detection, and for AGC voltage generation.

The phase detector output is amplified by U2B, whose time constant is approximately 15 milliseconds. The output of U2B is split and is fed in two directions: first through R39 to voltage comparator U4A where small amplitude variations in the signal are detected and provide the time code output.

The output of U2B also is fed through R89 to amplifier U2C which has an integrating time constant of approximately 25 seconds. The slowly varying output of U2C is used as the AGC voltage and is fed back to the RF amplifier to control the gain of the input stage.

Because the AGC voltage is derived from the output of a quadrature detector, it is present only after phase lock is achieved, and thus becomes the basis for a synchronous AGC. The gain of the amplifier in the front end of the receiver is running wide open until phase lock occurs. After phase lock is acquired the input amplifier gain is reduced to a level just sufficient to provide a reference for the phase locked loop and other stages in the A2 receiver assembly. Thus, no stages in the A2 receiver assembly are allowed to saturate or be overdriven in strong signal conditions.

Test point 3 is located at the reference voltage against which AGC amplifier U2C operates. Thus, the voltage measured from TP3 to TP6 is proportional to the input signal level, and can be used as a synchronous detector, or "lock-in voltmeter", as an indication of signal strength. If the antenna is adjusted and aimed to maximize this AGC voltage, optimum receiver operation is obtained.

The AGC voltage is also sent to voltage comparators U4B, U4C, and U4D as a means of indicating phase lock. When the AGC voltage measured between test points 3 and 6 rises to approximately 1.0 volt DC, the output of comparator U4B goes high turning off the red unlock panel indicator on the front panel. When lock is acquired and the green light goes on, the output of U4D goes high showing that phase lock has been acquired.

# 2.4.3 Phase Detector Balance Adjustment

The output of phase detector U1 for the phase locked loop control is balanced by adjustment of trimmer potentiometer R5. (See alignment procedure for A2 receiver assembly.) The output of the quadrature phase detector U3 is balanced by adjustment of trimmer potentiometer R30. (See alignment procedure for A2 receiver assembly.)

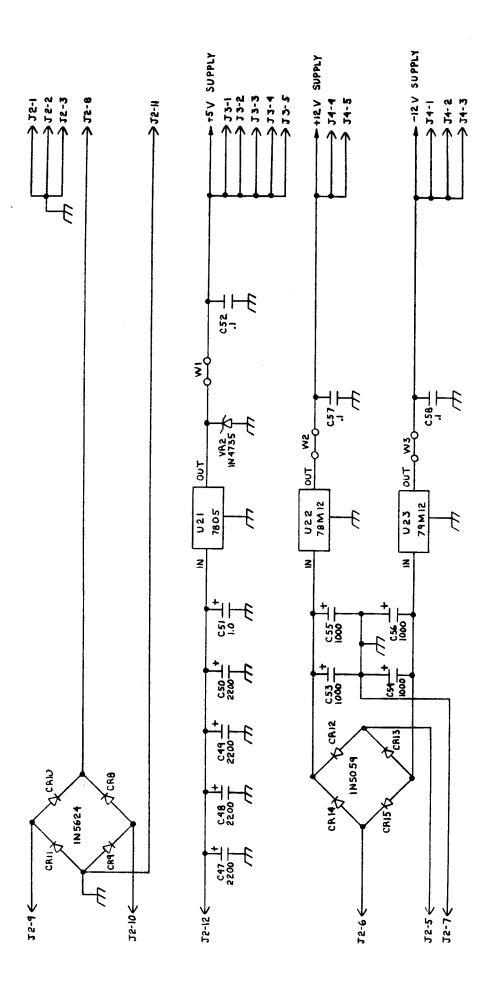

# 2.4.4 Power Supplies

Three-terminal regulators U21, U22 and U23 provide output voltages of +5.0 volts, +12.0 volts, and -12.0 volts. Because U21 which provides the +5.0 volts is the most heavily loaded of the voltage regulators, it is heat sunk to the chassis at the rear left corner of the circuit board. Regulators U22 and U23 are loaded more lightly and do not require heat sinking.

FIG. 2-4 SCHEMATIC - A1 RF AMPLIFIER

FIG. 2-5 SCHEMATIC - AZ RECEIVER - SHEET 1

FIG. 2-5 SCHEMATIC - A2 RECEIVER - SHEET 2

FIG. 2-5 SCHEMATIC - A2 RECEIVER - SHEET 3

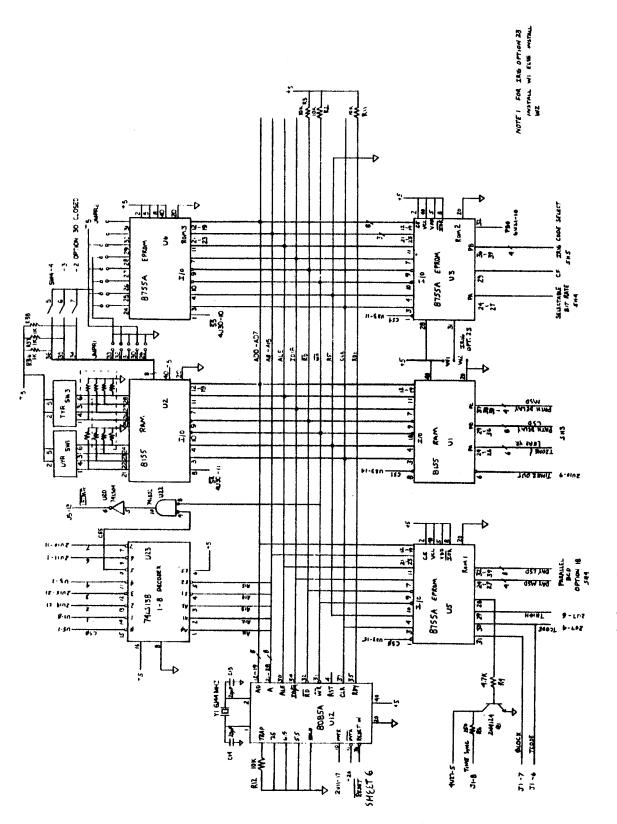

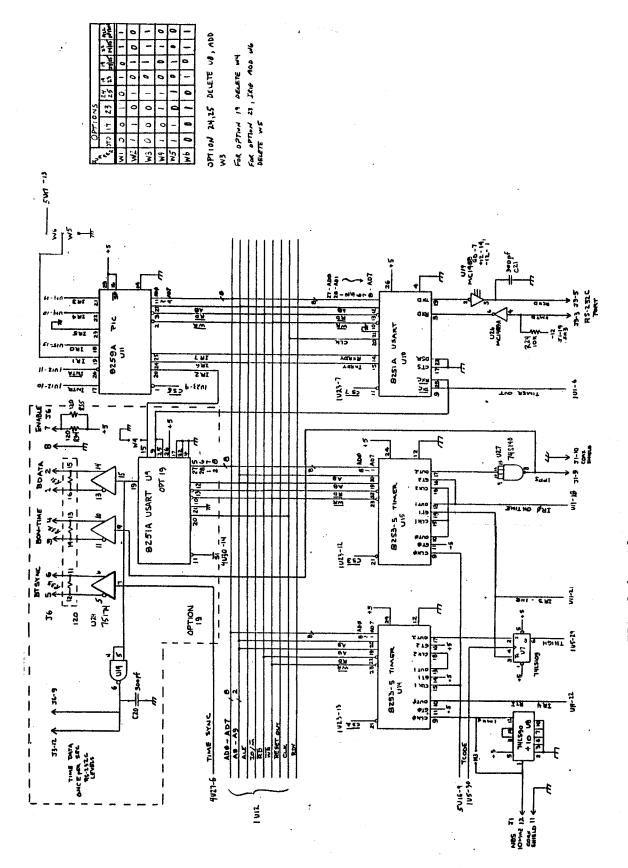

# 2.5 A3, MICROPROCESSOR ASSEMBLY, P/N 014800

The 10-MHz NBS phase locked signal is fed into U8 and divided by 10 to 1 MHz. (See Figure 2-3 Processor Block Diagram). This signal is divided by 5000 by U14A to provide a 200-Hz real-time interrupt, and it is divided by 1,000,000 by U14B and U14C to provide the 1-Hz on-time reference. It is divided by 100 by U15A to provide a 10-KHz signal which is fed as a clock input to path delay timer U15B. The path delay timer is gated on by the 1-Hz reference. An output pulse will occur after a delay proportional to the setting of the path delay thumbwheel switch on the rear panel. The signal is fed into U15C, which is a programmable one-shot. The output is a 100-millisecond pulse whose leading edge is "on-time".

The time code, TCODE, signal is fed to input U5-30 on the 8755A and to U8-4, the clock input to a 74LS109 J-K flip-flop. The TCODE is sampled at a 5-millisecond rate by the microprocessor. False noise pulses are discarded. The pulse widths are measured and decoded and the 1-Hz reference signal is phase locked to the leading edge of the time code.

The phase lock algorithm has two modes, fast sync and fine sync. In the fast sync mode, the 1-Hz reference is adjusted in 0.1-second steps until phase lock is achieved. The adjustment steps are progressively reduced to 1 millisecond. After the clock is set the steps are reduced to 0.1 millisecond. The time between adjustments is made progressively longer and will extend beyond 24 hours. Each time an adjustment is made the time and direction of the adjustment is logged in the Phase Adjust Table (See Section 1).

A serial RS-232 interface is provided by U10, 8251A USART and U26 and U19 level converters.

The program resides in U6, U5 and U3, 8755A EPROM & I/O. Variable data is stored in 512 bytes of RAM in U1 and U2 8155 RAM & I/O.

The processor runs under interrupt, with priorities controlled by U11 8259A Programmable Interrupt Control Chip.

The interrupt levels are:

IRO - On-time pulse

IR1 - Irig Frame Element (Option 23)

IR2 - Remote Output USART Xmit (Option 19)

IR3 - 1 Hz reference

IR4 - 200 Hz RTI

IR6 - USART Xmit

IR7 - USART Rcv

Chip selects are decoded by U23 and U30 8205 1-8 Decoder. The chip selects are:

| CSO - U5-1   | 8755A  | EPROM & I/O                       |

|--------------|--------|-----------------------------------|

| CS1 - U23-14 | 8155   | RAM 7 I/O                         |

| CS2 - U14-21 | 8253-5 | TIMER                             |

| CS3 - U15-21 | 8253-5 | TIMER                             |

| CS4 - U3-1   | 8755A  | EPROM & I/O                       |

| CS5 - U22-5  | 74LS02 | LED DISPLAY                       |

| CS6 - U11-1  | 8259A  | PROGRAMMABLE INTERRUPT CONTROLLER |

| CS7 - U10-1  | 8251A  | USART                             |

| SO - U4-6    | 8255A  | PROGRAMMABLE PERIPHERAL INTERFACE |

|              |        | (Option 18)                       |

| S1 - U9-11   | 8251A  | USART (Option 19)                 |

| S2 - U17-21  | 8253-5 |                                   |

| S3 - U16-21  | 8253-5 |                                   |

| S4 - U2-8    | 8155   | RAM & I/O                         |

| S5 - U6-1    | 8755A  | EPROM & I/O                       |

The central processing unit U12 is an 8085A with a 6.14-MHz crystal. Power-on reset is provided on pin 36 by a brown-out reset network. Signals RD, WR and RDY are tied to +5 volts through Resistors R3, R11 and R2.

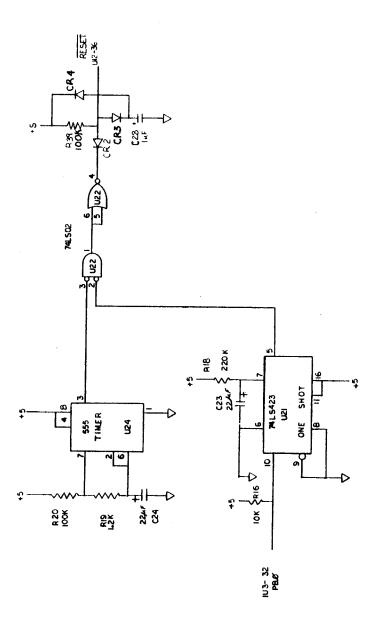

The 555 Timer, U24 sheet 6, is an Astable oscillator that generates a negative 20 millisecond reset pulse every 1.9 seconds. The retriggerable monostable multivibrator, U21B, is triggered once per second by a pulse that is generated by the program. The output of the one-shot inhibits the reset pulse from the Timer (Gate U22). On power up or if the normal program is stopped, the one-shot times out and a reset pulse is applied to the microprocessor.

The detail schematics for the Microprocessor boards are shown in Figure 2-6, sheets 1 through 6.

FIG. 2-6 A3 MICROPROCESSOR - SCHEMATIC - SHEET 1

FIG. 2-6 A3 MICROPROCESSOR - SCHEMATIC - SHEET 2

FIG. 2-6 A3 MICROPROCESSOR - SCHEMATIC - SHEET 3

FIG. 2-6 A3 MICROPROCESSOR - SCHEMATIC - SHEET 4

2-19

FIG. 2-6 A3 MICROPROCESSOR - SCHEMATIC - SHEET 6

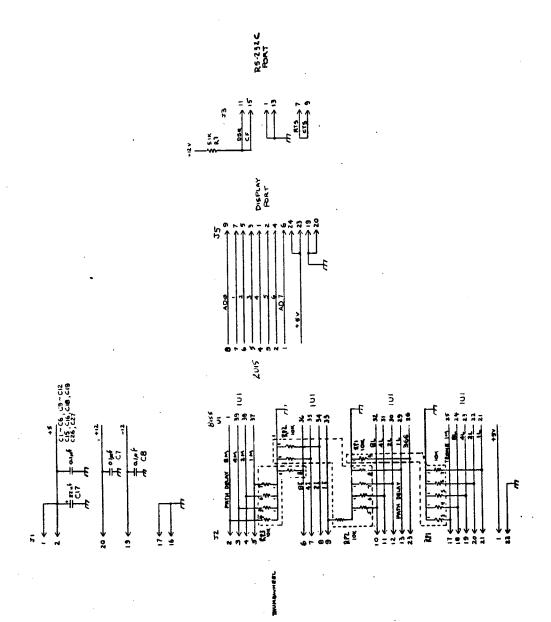

# 2.6 A4, DISPLAY ASSEMBLY, P/N 014100

The display assembly is mounted on the rear of the front panel. It consists of U7-ICM7218C LED Driver and six seven-segment LED digits that provide a 24-hour clock display (See Figure 2-7.)

## 2.7 POWER TRANSFORMER

The AC power schematic, Figure 2-8, shows the AC input for the +5 VDC, +12 VDC and -12 VDC power supplies. The AC input A6 is filtered by C1 and C2, then fed through fuse F1 and 115/230V switch S1 to transformer T1.

2-22

FIG. 2-8 AC POWER DIAGRAM

SECTION 3

8170

SERVICE INFORMATION

### 3.1 CALIBRATION OF THE MODEL 8170

The Model 8170 is "connected" to the National Bureau of Standards time standard via radio signals. The instrument automatically decodes the time transmitted by WWVB. Varification of proper operation can be made by tuning a HF receiver to WWVB and comparing the voice time announcements against the Model 8170. Alternatively, the audio portion of WWVB may be heard by calling 303-499-7111. Accuracy of the time signal received over the telephone is 30 milliseconds anywhere in the contiguous 48 states.

For precise calibration, a portable clock calibrated at NBS is required. Connect one trace of an oscilloscope to the On-time pulse output of the 8170 and the other trace to the On-time pulse from the portable clock. Set the path delay thumbwheel switch on the rear panel to 00.0. Synchronize the scope with the portable clock on-time pulse, adjust the path delay switch until the two pulses are coincident. The setting of the switch is the sum of the path delay and receiver delay in milliseconds.

In some applications it may be desirable to calibrate a group of clocks against one reference clock. This provides accurate relative time between the ensemble of clocks. The calibration procedure is the same as with the portable clock example, except an 8170 reference clock is used in place of the portable clock.

### 3.2 ALIGNMENT PROCEDURES

Figure 3-1 Assembly drawing shows the location of the major assemblies.

### 3.2.1 RF Amplifier Assembly (A1 Board, Figure 3-2)

- 1. Disconnect the AGC wire (violet) from Connector A1P2 pin 6, but leave the remaining wires in place and the connector mated.

- 2. Connect an oscilloscope probe to A2E1. Set the scope for AC coupling. The ground lead is connected to the chassis.

- 3. Connect a signal generator to the antenna input of the receiver. Set the generator to provide a 1.0 uV signal at exactly 60,000 Hz, unmodulated.

- 4. Apply power to the receiver and adjust the signal generator level as necessary to provide a 1 volt p-p output signal on the oscilloscope.

- 5. Adjust the slug in transformer A1T1 for a peak on the oscilloscope, while reducing the signal generator level to maintain the 1V p-p output.

FIG. 3-1 ASSEMBLY DRAWING - MAINFRAME

FIG. 3-2 A1 RF AMPLIFIER ASSEMBLY

- 6. Adjust capacitor A1C8 for maximum output on the scope.

- 7. Readjust the signal generator frequency to 100,000 Hz and increase the output for a reading of 1V p-p on the oscilloscope (Do not exceed 0.1 volt at the antenna input).

- 8. Adjust capacitor A1C9 for minimum output on the oscilloscope, while increasing the signal generator level to maintain 1V p-p output (Do not exceed 0.1 volt at the antenna input).

- 9. Readjust the signal generator output frequency to 60.000 KHz at a 1 mV level.

- 10. Synchronize the oscilloscope, and observe the output waveform and level. The output should be a square wave with a 40-60% duty cycle and 3V p-p  $\pm$  20% amplitude.

- 11. Set the signal generator output level at 5 uV. The oscilloscope amplitude should equal or exceed 1.5V p-p (the output will be a sine wave until the clipping point is reached at approximately 3V p-p).

- 12. The AGC Alignment is performed as described in step 17 of the Receiver Assembly (A2 board) procedure described below.

- 13. Disconnect the oscilloscope and signal generator.

### 3.2.2 Receiver Assembly (A2 Board, Figure 3-3)

- 1. Connect a clip lead from A2E2 to A2E3. Connect the negative lead of a DVM to test point A2TP3 and the positive lead to test point A2TP4. Set the DVM for a full scale range of  $\overset{+}{}$  2V. There should be no connection to the antenna input at this time.

- 2. Apply power to the receiver. The DVM should read zero  $\pm$  5 mV. If the voltage error is greater than  $\pm$ 5 mV, adjust potentiometer A2R30. Some variation will be noted, but it should be less than  $\pm$  5 mV.

- 3. Move the positive DVM lead from test point A2TP4 to A2TP6. The reading should be less than 500 mV. Glyptol A2R30 if it has been adjusted.

- 4. Move the positive DVM lead to test point A2TP2 and the negative DVM lead to A2TP1.

- 5. The DVM reading should be zero ±5 mV as observed in step 2 above. If the voltage error is greater than ±5 mV, adjust potentiometer A2R5.

- 6. Remove both DVM leads from the test points and turn off the receiver.

- 7. Move the clip lead from A2E3 to A2E4 (A2E2 jumpered to A2E4). Connect the positive lead of a 0-1 mA meter to A2J1-10.

- 8. Apply power to the receiver. The meter should read 0.8 mA. If it does not, adjust potentiometer A2R14. Glyptol A2R14 if it has been adjusted.

- 9. Connect a frequency counter to the 10 MHz NBS output on A2J1-13. The counter should read 9,999.900 KHz (9.999900 MHz). If necessary, adjust capacitor A2C10 to obtain this reading. Disconnect the frequency counter and the clip lead from A2E2 to A2E4.

- 10. Connect the 10 MHz NBS output on A2J1-13 to a spectrum analyzer or selective voltmeter through a suitable attenuater.

- 11. Adjust potentiometer A2R23 for a minimum 2nd harmonic (20 MHz) on the spectrum analyzer. It should be adjustable to at least -20 dB relative to the 10 MHz output. Glyptol A2R23.

- 12. Connect a signal generator to the receiver antenna input, set a 1 mV output at 60.000 KHz unmodulated. The receiver should lock to this signal as indicated by the green lock lamp being lit. Measure the VCO lock voltage by connecting the positive lead of a 0-1 mA meter to A2J1-10. If necessary, adjust capacitor A2C10 very slowly until the lock voltage is exactly at center scale.

- 13. Disconnect the signal generator from the receiver antenna input and note the lock voltage meter reading on the milliammeter (disregard any sudden small jump at the moment of disconnection). If a downward drift is observed, adjust A2R5 clockwise by very small amounts until the drift is stopped (small jumps may occur as the potentiometer is adjusted, disregard these and note only the slow drift). Conversely, if an upward drift is observed, adjust potentiometer A2R5 CCW by very small amounts until the drift is stopped. This is a very fine adjustment, and is completed when no perceptible drift is evident after one minute of observation. Glyptol the potentiometer if it has been adjusted.

- 14. Connect the signal generator to the receiver antenna input and set it for a 1.0 microvolt level at 60.000 KHz, unmodulated.

FIG. 3-3 A2 RECEIVER ASSEMBLY

- 15. Connect the negative lead of a DVM to test point A2TP3. Select a scale in the +5 to +20 VDC range and connect the positive lead to test point A2TP6. The reading should increase to greater than 2.38V after the receiver has locked (green light on). Lock-up may take several minutes at the 1.0 uV input, and the voltage at test point A2TP6 may continue to rise after the green lock light has lit.

- 16. After the voltage at the above test point has exceeded +2.38V, decrease the signal generator output level by small amounts (less than 1 dB) until the voltage has decreased to +2.38V. When approaching the correct voltage it will be necessary to wait one minute or more between signal generator level changes, as the voltage read on the DVM is delayed by a 90-second time constant from the initiation of change. A +2.38V reading at test point A2TP6 is normally reached with an antenna input level between 0.25 and 1.0 uV.

- 17. Without changing the signal generator level from that obtained in step 16 above, reconnect the violet AGC wire to pin 6 of connector A1P2 (see step 1, RF Amplifier Assembly). The DVM reading will slowly decrease and stabilize at +1.38 volts. If the DVM stabilizes at a different reading, adjust the AGC control potentiometer, A1R19, on the RF Amplifier Assembly (A1) in very small amounts until the meter reading stabilizes at 1.38 volts. A wait of one minute or more between pot settings may be necessary due to the long time constant described above. If potentiometer A1R19 has been adjusted, apply glyptol.

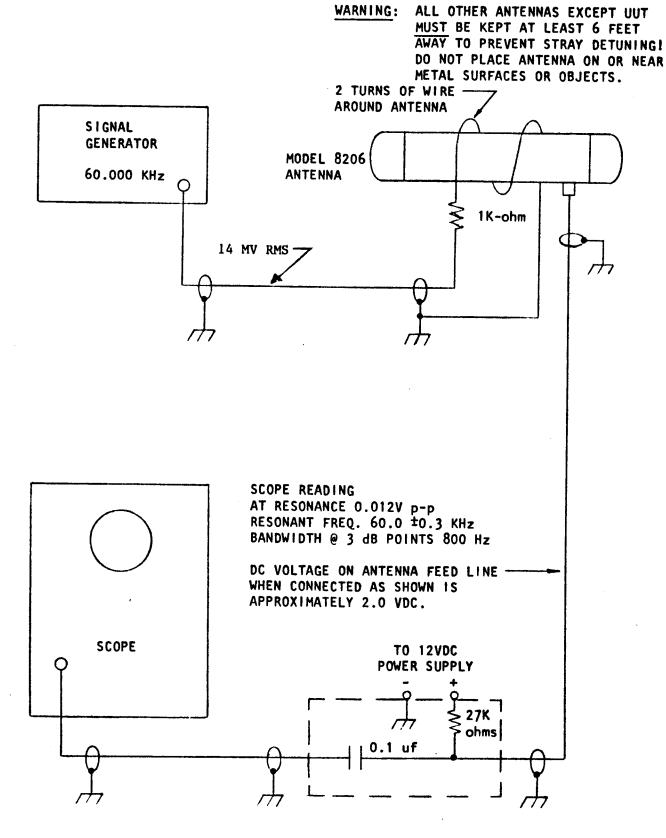

# 3.3 ANTENNA (Model 8206) TEST PROCEDURE (Fig. 3-4)

- 1. Connect a length of coaxial cable to the output connector of a signal generator.

- 2. Wrap 2 turns of wire around the antenna. Connect one end of the wire to the coaxial cable shield. Connect the other side to a 1 K ohm resistor. The other side of the resistor is connected to the center conductor of the cable as shown in Figure 3-4.

- 3. Adjust the signal generator for an output of 60.000 KHz at 0.007 V RMS (0.014 volts behind 50-ohms).

- 4. Connect the output connector of the antenna to the oscilloscope as shown in the figure, with an 0.1 uf capacitor in series with the scope input.

- 5. Connect a 12 VDC power supply to the antenna output through a 27K ohm series resistor.

- 6. The oscilloscope shall display a 60.0  $\pm$ .3 KHz resonant frequency at an amplitude of approximately 12 mV p-p and a bandwidth at the 3 dB points of approximately 800 Hz.

FIG. 3-4 ANTENNA MODEL 8206 TEST SETUP

# 3.4 <u>MODEL 8207 - ANTENNA PREAMP ALIGNMENT</u> (requires an operating receiver)

- 1. Disconnect the receiver AGC wire (violet) from connector AlP2 by removing pin 6 from the connector. Be sure that pin 6 cannot make contact with any other circuits during the following tests, but leave the remaining wires in place and the connector mated with A2J5. Perform Receiver RF Amplifier Alignment Steps 2 through 8 only if not previously aligned.

- 2. Turn off the receiver and disconnect the signal generator. Connect the output of the antenna preamplifier to the receiver antenna input. Set receiver AlS1 to the preamp (right) position. Connect the signal generator output to a 40 dB pad. Connect the pad output to the preamp input through the network shown below.

FIGURE 3-5 ANTENNA PREAMP ALIGNMENT SETUP

- 3. Align 8207 Preamp by performing RF Amplifier Alignment procedure steps 1 through 5. Adjust Preamp T1 instead of receiver AlT1.

- 4. Perform RF Amplifier Alignment procedure step 12.

- 5. Reconnect the violet wire on the receiver at AlP2-6.

NOTE: When performing this alignment, the Model 8207 preamp must be physically separated from the receiver by at least 10 feet using a long coaxial cable. Keep the cable from the signal generator to the preamp away from the vicinity of the receiver to prevent system regeneration.

#### 3.5 TROUBLE SHOOTING

- 3.5.1 RECEIVER If trouble occurs with a WWVB receiver, some simple checks can isolate the problem to specific areas of the receiver. Some of the more likely problems and the procedures for solving them are as follows:

- 1. RECEIVER DOES NOT LOCK. Improper reception. The most efficient way of solving this type of problem is to isolate the problem to one of the three major receiver system components. These are antenna, A1 RF Amplifier assembly, and A2 receiver board assembly.

- A. Antenna DC check. Measure the DC voltage on the antenna line with a DVM. With the antenna connected to the receiver and the receiver turned on, the DC voltage on the coaxial line should be approximately +2.0 volts ± 10%. This can be measured by inserting a coaxial tee in the line at the rear of the receiver and measuring the antenna voltage with the antenna connected. With the antenna disconnected the DC voltage at the antenna terminal of the of the receiver should be approximately +11.5 volts DC ±10%. If both these measurements are satisfactory, proper DC conditions are verified in both the antenna and its power supply in the receiver.

If the +11.5 volt level is not present with the antenna disconnected, the fault is in either the A1 RF amplifier assembly or in the A2 Receiver assembly. Disconnect the A1 board and check for +12 VDC at pin 1 of the connector A1P2. If the voltage is not present, the problem is in the power supply on the A2 board assembly (diodes CR12 through CR14, capacitors C53 through C57, or regulator U22). If the +12 volt level is present, the problem is in the A1 board assembly.

B. Check the receiver without the antenna connected. Using a signal generator set at 60.000 KHz with an accuracy of ±1 x 10<sup>-6</sup>, feed a 1.0 microvolt signal from the generator to the antenna input of the receiver and see if the receiver locks. If it does lock under this condition, the problem is most likely with the RF performance of the antenna or with the antenna placement or installation. If the receiver does not lock with 1.0 microvolt applied, the fault is in the receiver. Check the 60 KHz signal at E3 of RF amplifier board A1. If the signal is present, the RF amlifier is operating satisfactorily and the problem is in Receiver assembly board A2. If the 60 KHz signal is not

present at E3, the fault is in the A1 board assembly.

- 2. NO 1-MHZ NBS OUTPUT AT REAR PANEL JACK. Check pin 11 of U5A on A2 board to see that the oscillator stage containing A2Y1 is operating properly, and oscillating at 10.0 MHz. If this oscillator, which gets phase locked to WWVB, is not oscillating then the most likely problem is with the crystal Y1, which may need to be replaced. Another possibility is oscillator alignment. If this oscillator stage is not performing properly, the NBS output will not be present, and the receiver will not phase lock, or alternatively the phase lock lamp may remain on continuously even though the receiver is not operating properly. This condition can be checked by removing the antenna signal and checking to see that the phase lock lamp is extinguished after approximately 30 seconds. See section 3.2.2 paragraph 12 for instructions on oscillator alignment.

- 3. FUSE BLOWS. This problem is probably caused by power supply malfunction in the A2 board or in the chassis power supply components such as power transformers, filter capacitors, etc. The problem may be isolated to on or off-board causes by disconnecting all of the connectors from the A2 board and turning the unit on again. If the fuse still blows the cause is not on the A2 board. If the fuse does not blow with the connectors removed from the A2 board, reconnect them in the following order, turning power on after each connector is reattached:

- A. Reattach the connector from the cable harness to A2J2. This connects the power transformers to the power supply rectifier circuits. If this causes the fuse to blow, the problem is probably a power supply short on the A2 board itself. Check the voltage regulators U21, U22, and U23 for proper operation. Check to see that Zener diode VR2 is not shorted to ground. This diode provides over-voltage protection on the +5 VDC line and will fuse, shorting to ground causing a fuse to blow if U21 fails and lets the +5 volts go high. Before replacing VR2, disconnect both VR2 and jumper W1 and check U21 for proper operation. If connecting the cable at A2J2 does not cause the fuse to blow after the power is reapplied, proceed to the next step.

- B. Connect the A1 assembly to A2J5. Reapply power.

- C. Connect the cable harness connector to A2J1. Reapply power. If this causes the fuse to blow, the problem is probably in the A3 or A4 assemblies.

.

D. Reconnect the cables at A2J3 and A2J4. A2J3 provides +5 volts DC to the other parts of the receiver, including the front panel and a short on one of these lines will cause a fuse to blow.

## 3.5.2 Microprocessor

1. VOLTAGE CHECKS - Measure the +5, +12, and -12 voltages at the microprocessor board. The +5 should be 4.75 to 5.25 volts. The ±12 should be nominal voltage ±1 volt.

If the voltage is incorrect, check the power supply.

2. DIVIDER CHAIN - The 10 MHz signal from the receiver is divided down by U8, U14 and U15. Check the following pins for the proper signal:

U8-14 - 10 MHz U14-17 - 1 Hz U8-11 - 1 MHz U15-1 - 10 KHz U14-10 - 200 Hz

## 3.6 MICROPROCESSOR AND DISPLAY ASSEMBLY

Figure 3-6 shows the component locations for the Display Board.

Figure 3-7 shows the component locations for the Microprocessor Assembly.

FIG. 3-6 ASSEMBLY DRAWING - DISPLAY BOARD A4

# SECTION 4

# MODEL 8170 OPTIONS

| Option 15    | - | Timing Pulse Outputs               |

|--------------|---|------------------------------------|

| Option 18    | - | Parallel BCD Output                |

| Option 19    | - | Remote Output Driver               |

| Option 23    | _ | IRIG B Output                      |

| Option 24,25 | - | TCXO and External Oscillator Input |

| Option 28    | _ | 1 KHz Output                       |

| Option 30    |   | Fully Decoded Text Stream          |

# 4.1.0 OPTION 15 - TIMING PULSE OUTPUTS

Option 15 provides 60-Hz and 1-Hz TTL signals that are phase locked to the WWVB carrier. The 60-Hz signals is fed out on pin 49 of the rear panel 50-pin connector. The 1-Hz signal is fed out on pin 48. Pin 46 is ground for Option 15.

The signals are TTL-compatible square waves, each capable of driving a 93-ohm resistive load.

With normal signal reception the typical long-term timing accuracy is nominally 1 x  $10^{-11}$ ; short term accuracy is 1 x  $10^{-5}$  typical.

#### 4.1.1 OPTION 15 - PRINCIPLES OF OPERATION

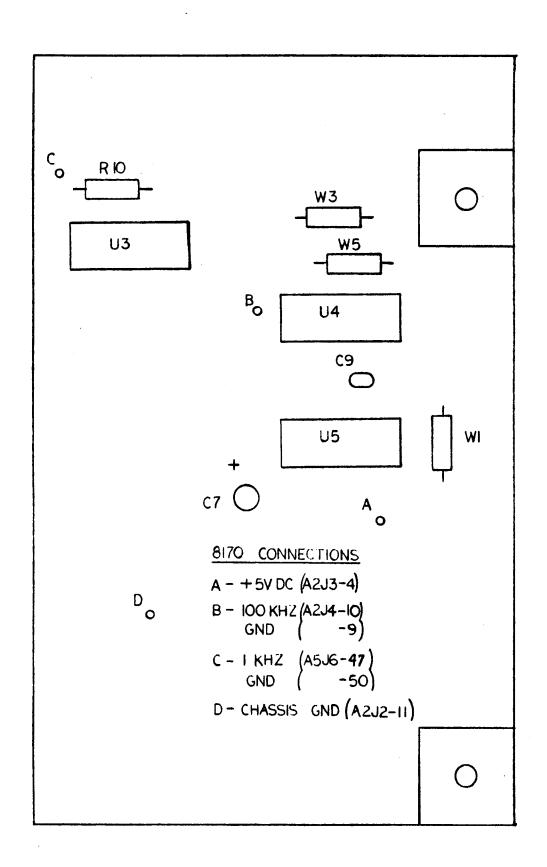

The schematic for Option 15 is shown in Figure 4-1. The assembly drawing is shown in Figure 4-2.

The board is physically located between the front panel and assembly A2. The NBS 100 KHz input signal at A7J1-1 originates at A2J-12. It is divided by 5 by U1 and multiplied by 3 by the tripler. This 60-KHz signal is divided by 1000 by U2, U3, and U4 and the resulting 60-Hz signal is fed out by U7-8. Dividers U5 and U6 divide the 60-Hz signal by 60 and the 1-Hz signal is fed out on U7-6. These signals are wired to the rear panel 50-pin series D connector. The 60-Hz signal is on A5J6-49 and the 1-Hz signal is on A5J6-48. The ground return is pin A5J6-46.

FIG. 4-1 OPTION 15 SCHEMATIC

FIG. 4-2 OPTION 15 ASSEMBLY DRAWING

# 4.2.0 OPTION 18 - PARALLEL BCD OUTPUT

The Parallel BCD Option provides the day and time data in parallel BCD format on a 50-pin series D female connector (DD 50S). The connector is located on the rear panel. All lines are TTL-compatible and will drive one TTL load.

Data is valid 20 milliseconds before the ON-TIME pulse and remains valid until 850 milliseconds after the ON-TIME pulse.

All signals are positive logic: a logical 1 is a high, a logical 0 is a low.

The signal names and pin numbers are listed below. 8-4-2-1 BCD weighting is indicated in the mnemonic.

| SIGNAL      | MNEMONIC | PIN                 |

|-------------|----------|---------------------|

| Hours MSD   | нвм      | A <del>5</del> J6−1 |

| 11          | H4M      | A5J6-2              |

| tt          | H2M      | A5J6-3              |

| 11          | H1M      | A5J6-4              |

| Hours LSD   | H8L      | A5J6-5              |

| 11          | H4L      | A5J6-6              |

| 11          | H2L      | A5J6-7              |

| 11          | H1L      | A5J6-8              |

| Minutes MSD | M8M      | A5J6-9              |

| tt          | M4M      | A5J6-10             |

| 11          | M2M      | A5J6-11             |

| Ħ           | M1M      | A5J6-12             |

| Minutes LSD | M8L      | A5J6-13             |